Check out our full list of Verilog based projects!

Verilog® HDL: Project 1

Learning relevant keywords and concepts

Project Overview

The goal of this project is to learn about the components inside of a Verilog project (but not program an FPGA quite yet, that's the next project). If you have not already installed Vivado, you can find a guide to do so here. If you are hoping for a Project 0 where you learn how to navigate the Vivado interface in the first place, we highly recommend the Getting Started with Vivado Guide.

A list of the all of the Verilog projects can be found here.

Remember that we won't be adding any files or creating a bitstream for this first project; that'll all start in Project 2. If you have any questions after reading through the project, please feel free to post them on the Digilent Forum where an engineer will be happy to assist you.

What is a Verilog® Module?

A Verilog® module of a circuit encapsulates a description of its functionality as a structural or behavioral view of its input-output relationship. A structural view could be as simple as a netlist of gates or as complex as a high level architectural partition of the circuit into major functional blocks, such as an arithmetic and logic unit (ALU). A behavioral view could be a simple Boolean equation model, a register transfer level (RTL), or an algorithm. This tutorial will look at the basics of a Verilog file.

A Simple Example

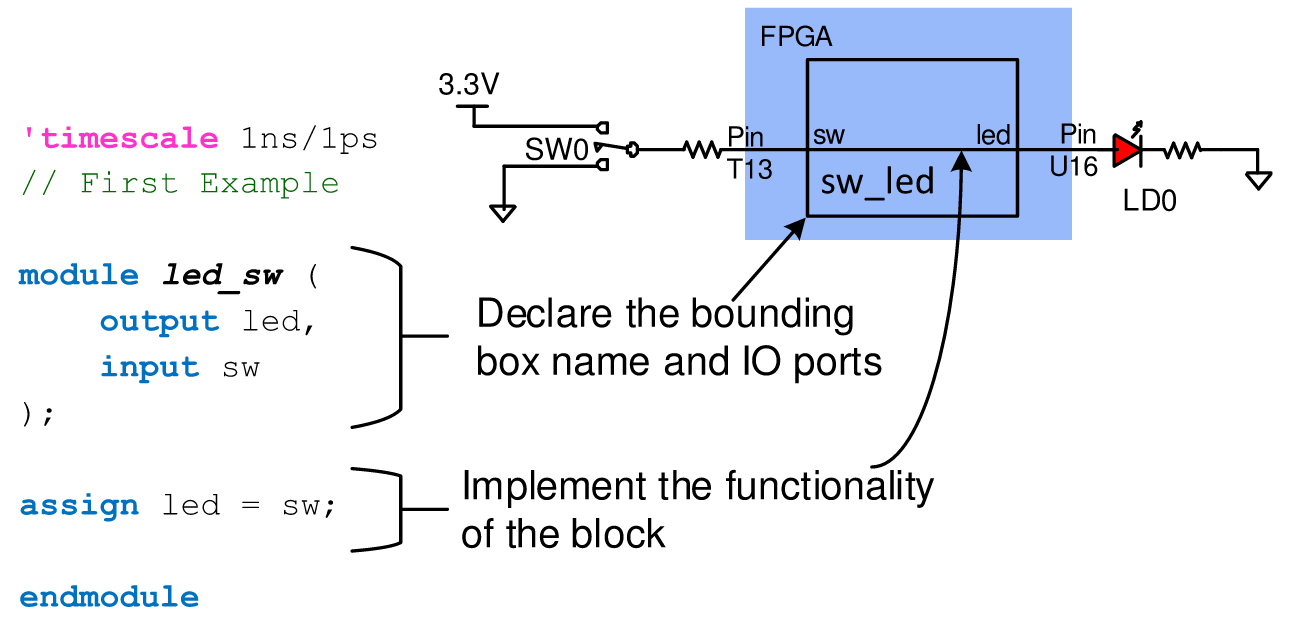

The general format for a Verilog® circuit is shown in the code in the picture below. Major keywords have been shown in blue, comments in green, Verilog requirements in pick, and key text strings the user must supply are shown in bolded italics. We will then go through each of the lines in detail to learn about what they do.

Timescale

This timescale is required for all Verilog projects to synthesize correctly. If you had multiple types of delays, multiple timescales may be listed.

Module

In a schematic capture environment, a graphical symbol defines a given logic circuit by showing a “bounding box” as well as input and output connections. In Verilog, this same concept is used, only the bounding box must be explicitly typed into the text editor, starting with module and ending with the phrase endmodule.

The module block (as shown in the image) gives the circuit a name (“led_sw” for readibility, it could have been called “myFirstModule123abc”) and defines all input and output ports, effectively playing the same role as a symbol in a schematic environment. The module is closed by an endmodule statement, and all the statement between module declaration and endmodule describes the functionality of the module, i.e., the internal circuit connection of the module.

In terms of syntax, the inputs and outputs of the named module are enclosed by a set of parenthesis () with a semicolon ; and with a comma , between each set of inputs/outputs. An example is provided below:

module inputOutput( input inputExample, output outputExample, input [2:0] 3inputs, output [7:0] 7outputs ); endmodule

If a set of inputs/outputs is actually a bus (an array), a set of square brackets [] is used around a range of numbers in the form [MSB:LSB]. No special syntax is needed to end the module, just the word endmodule.

Input, Output, and Bus

Whenever you are writing a Verilog module, the first thing to do is to define the input and output signals. In the example in Fig. 1, there is one input signal “sw” coming from the onboard switch SW0, and one output signal “led” connected to LED0. How did we choose the names “sw” and “led”? They came from the XDC file.

Note, however, that input and output can be a group of wires as well. We call these groupings a bus. To declare the input or output as a bus, we need to provide the CAD tools with the index of the most significant bit (MSB) of the bus and the index of the least significant bit (LSB) of the bus. For example, the following code defines an 8-bit wide bus “sw”, where the left-most bit (MSB) has the index 7 and the right-most bit (LSB) has the index 0, with a colon : separating the two numbers.

input [7:0] sw

Indexing a bus in Verilog is similar to indexing an array in the C language. For example, if we want to index the second bit of sw bus declared above, we will use sw[1]. No semicolon is used while listing the various inputs and outputs that are used.

Assign

The assign statement in the example above assigns the signal value on the net “sw” to the net “led”. In implementation, it creates a wire that connects the input port sw to the output port led.

An assign statement can also be used to assign one signal of a bus to one signal of another bus. For example, if we declared sw as an 8-bit wide bus and LED as an 8-bit wide bus, and we want to use second switch to control fourth LED, the code will be:

module led_sw( output [7:0] led, input [7:0] sw ); assign led[3] = sw[1]; ... endmodule

At the end of each assign statement (can be more than one line long), a semicolon ; is required.

Constants

You can also assign a constant number to a signal or a bus to tie them to either logic '1' (VDD) or logic '0' (GND). The basic syntax for a constant number in Verilog is (including the apostrophe):

<Width in bits>'<base letter><number>

Some examples:

| Constant in Verilog | Explanation | Value in Binary |

|---|---|---|

| 12'h1e3 | Hexadecimal 123 represented with 12 bits | 0001 1110 0011 |

| 20'd44 | Decimal 44 represented with 20 bits | 0000 0000 0000 0010 1100 |

| 4'b1010 | Binary 1010 represented with 4 bits | 1010 |

Important Takeaways from Project 1

- Module in Verilog HDL acts like the bounding box in circuit schematic.

- Bus is a group of signals (wires).

- Assign statement passes the value of a signal/bus to another signal/bus.

- Constant in Verilog HDL is presented in form of <Width in bits>'<base letter><number>

- A desire to check out Project 2 where we actually program the FPGA

tags to be added via the tag> and double curly braces around everything

learn programmable-logic software tutorial vivado