Switch Controlled LEDs

Project 2: Use Switches to Control LEDs

This project demonstrates how to use Verilog HDL with an FPGA board. In this project you will use a switch on your FPGA board to turn on an LED. In doing this, you will learn the first steps of writing Verilog code and observe how a switch can control LEDs on an FPGA board. You won't need to have a really thorough understanding of digital engineering to make this project work; however, if you would like to know the inner workings of the digital circuit, more information is available in Project 1.

Prerequisites

- Have the Xilinx® ISE WebPACK™ installed.

- Have your FPGA board set up.

Software

- Xilinx ISE WebPACK.

Hardware

Background Knowledge

Related Material:

Basic Input/Output Devices

Printed Circuit Boards

Connectors

Integrated Circuits

Introducing Verilog

Verilog: The First Example

A Digital circuit contains a power supply, devices, and conduction nets. Some nets provide the circuit with inputs from the “outside world,” while others, conversely provide information from the circuit to the outside world. The nets that provide an interface between the circuit and the outside world are called ports.

Circuits need input devices to generate input signals. Input devices can take many forms, among them keyboards (such as on a PC), buttons, and switches. Circuits also need output devices to communicate their state to the user. In this project, a switch is used as the input device and an LED is used as the output device.

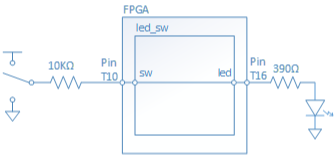

The digital circuit we will build is called the “led_sw,” as shown in Fig. 1 below. The circuit created in this project will be implemented inside the FPGA board. The board has an input port called “sw,” which receives an input signal from the external switch in the circuit and an output port called “led,” which drives the external LED in the circuit. The “led_sw” is a simple circuit that bypasses the signal on the input port and directly sends information to the output port. You can view this as a direct wired connection between the net “sw” and the net “led.” The circuit will be implemented using Verilog HDL. On different FPGA boards, switches and LEDs are connected to different pins on an FPGA chip. Thus, a user constraint file (UCF) is needed to map the input and output net of the circuit to the physical pin location on the FPGA chip. Take Nexys 3 as an example, the Slide Switch 0 (SW0) is connected to FPGA pin T10, and FPGA pin U16 drives LED 0 (LD0).

When you slide the switch to the ON position, a high voltage will be placed on FPGA pin T10, which is mapped to the input port of the circuit “led_sw.” The digital circuit then transmits the signal onto the output port LED, which is connected to FPGA pin U16. The high voltage on the output port “led” will cause a voltage drop between node A and node B. This voltage drop will drive current through the LED, which will light the LED and inform the user that the switch is on.

Procedure

1. Create a new project

- Create a Verilog module as explained in the previous project, which can be accessed through the link provided at the right, and name it “led sw”.

- Once you have created the module an inputs and outputs setting page will appear.

- Add “sw” as an input; ignore the “bus,” “MSB,” and “LSB.”

- Add “led” as an output; ignore the “bus,” “MSB,” and “LSB.”

2. Design the Circuit in Verilog HDL

In step 1, a template has been generated by the Xilinx tools as follows:

module led_sw( output led, input sw );

In this code, you have demonstrated that the net “led” is the output and the “sw” is an input. Now it is time to implement the circuit. At this time we will use an “assign” statement in Verilog to connect the output port “led” to the input port “sw”. The “assign” statement is used so that whenever a signal is placed on the input net it will be transmitted directly to the output port.

assign led = sw;

Lastly, you must always make sure to end the module with the “endmodule” code. When you have completed this project file it should look like this:

'timescale 1ns/1ps module led_sw( output led, input sw ); assign led = sw; endmodule

3. Create a User Constraint File (UCF)

The circuit has been implemented but the Xilinx tools still need to know what physical pins on the FPGA the input and output ports are mapped to. The UCF file will give the tools for this information. Please view the code sections below to find the UCF file corresponding to your board, as pin locations vary from board to board:

Nexys 4

Net "sw" Loc=U9; Net "led" Loc=T8;

Nexys 3

Net "sw" Loc=T10; Net "led" Loc=U16;

Nexys 2-500

Net "sw" Loc=G18; Net "led" Loc=J14;

Nexys 2-1200

Net "sw" Loc=G18; Net "led" Loc=J14;

Basys 2

Net "sw" Loc=P11; Net "led" Loc=M5;

You can find the location you need from the schematic of your FPGA board, or you can download the master UCF for your board from the Digilent website and copy the corresponding lines for this step.

4. Generate Bit File and Test it on FPGA Board

Double-click on “Generate Programming File” to generate the bit file and download it to your FPGA board. After you program your board, you can slide on the SW0 on your board to turn on LD0.

Test Your Knowledge

Now that you've completed this project, try these modifications:

- In this project, we used only one switch to control one LED. You can modify the code a little bit and use all 8 switches on your board to control the 8 LEDs. To do so, you would assign SW0 to control LD0, SW1 to control LD1, and so on.

- Now think of a way to modify your project a little bit to change which switch controls which LED. For example, make SW0 control LD6.