Pmod LVLSHFT

Buy

Reference Manual

Technical Support

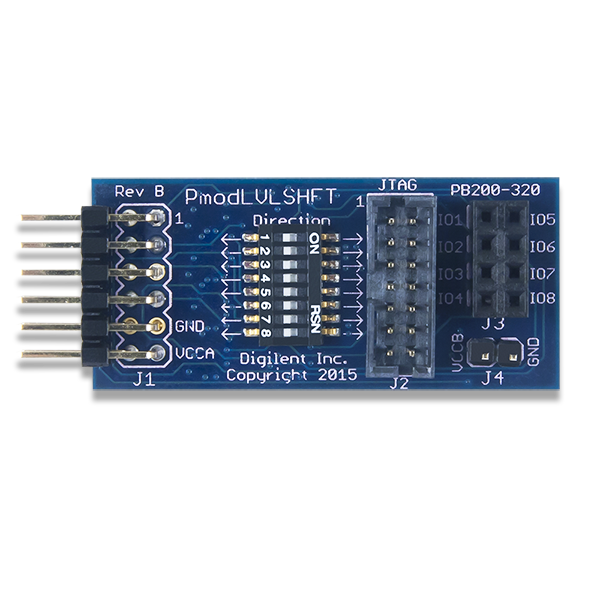

Pmod LVLSHFT

Logic Level Shifter

Features

- Digital logic level shifter

- Translate logic signals between two user supplied voltage levels

- 2×7 JTAG header

- 8 miniature switches to dictate logic level conversion

- Voltage range between 1.8V and 5.5V

- 12-pin Pmod port with GPIO interface

- Follows the Digilent Pmod Interface Specification

Physical

Width

1.75 in (4.45 cm)

Length

0.80 in (2.03 cm)

Design Resources

3D CAD file

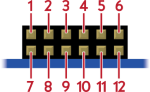

J1 Pinout

Pin 1

AIO1/TMS

Pin 2

AIO2/TDI

Pin 3

AIO3/TDO

Pin 4

AIO4/TCK

Pin 5

GND

Pin 6

VCCA

Pin 7

AIO5

Pin 8

AIO6

Pin 9

AIO7

Pin 10

AIO8

Pin 11

GND

Pin 12

VCCA

J2 Pinout

Pin 1

GND

Pin 2

VCCB

Pin 3

GND

Pin 4

BIO1/TMS

Pin 5

GND

Pin 6

BIO4/TCK

Pin 7

GND

Pin 8

BIO3/TDO

Pin 9

GND

Pin 10

BIO2/TDI

Pin 11

GND

Pin 12

NC

Pin 13

GND

Pin 14

SRST

J3 Pinout

Pin 1

BIO1/TMS

Pin 2

BIO5/SRST

Pin 3

BIO2/TDI

Pin 4

BIO6

Pin 5

BIO3/TDO

Pin 6

BIO7

Pin 7

BIO4/TCK

Pin 8

BIO8

J4 Pinout

Pin 1

VCCB

Pin 2

GND

Example Projects

- Digilent Pmod IPs are only supported in Vivado and Xilinx SDK versions 2019.1 and earlier.

Programmable Logic

- No programmable logic example projects are available for the Pmod LVLSHFT

Additional Resources

- Specification Version 1.2.0: PDF