Vivado Library

Overview

Vivado Library is, as its name states, a library that contains free-to-use IP cores and interface definitions compatible with Xilinx Vivado IP Catalog.

Due to the fact that it's a library constantly updating and changing, adding new IPs or features, it is recommended to periodically check the Github repository's releases page to find the latest release. Alternatively, you can download the latest set of sources here: vivado-library-master.zip.

This GitHub repository contains a large number of IP cores intended for use with Digilent boards, including all of Digilent's Pmod IP cores and Pmod interface descriptions.

Installation Guide

Steps for including the Vivado Library in your projects:

Download the vivado-library-<version>.zip file (NOT one of the source code archives!), then extract this archive in a location to remember.

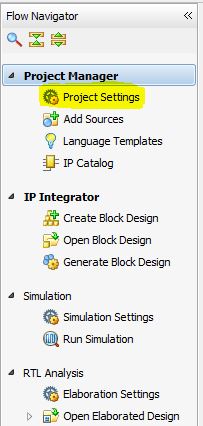

Click Project Settings under Project Manager.

IPcores

- AXI_DPTI_1.0 - this core implements an interface between DPTI and AXI4 Stream. The interface will be controlled using Microblaze via control and status registers and it will theoretically be capable of speeds up to 480 megabits per second. More details about its functionality can be found in the documentation

- MIPI_CSI_2_RX - This IP is compatible with CSI-2 1.0 specifications and supports decoding selected pixel formats and packing data into an AXI-Stream. It pairs up with a MIPI D-PHY Receiver IP over the standard PHY Protocol Interface (PPI) to source a video subsystem. More details about its functionality can be found in the documentation

- MIPI_D_PHY_RX - This IP is compatible with D-PHY 1.0 specifications and serves as the lowest layer of the high-speed source-synchronous interface defined by MIPI Alliance. It pairs up with a MIPI CSI-2 Receiver IP over the standard PHY Protocol Interface (PPI) to receive data from an image sensor and source a video subsystem. More details about its functionality can be found in the documentation

- Pmods - It contains a set of IPs for most of the Digilent Pmods

- Sync_v1_0 - It provides clock domain crossing for signals where variable crossing latency does not affect functionality. More details about its functionality can be found in the documentation

- Zmods - It contains a set of low level controller for both ZmodADC1410 and ZmodDAC1411, as well as their corresponding AXI interface adapters.

- axi_ps2_1.0 - The purpose of this IP is to implement a software controllable PS/2 host controller. More details about its functionality can be found in the documentation

- dvi2rgb - This IP interfaces directly to raw transition-minimized differential signaling (TMDS) clock and data channel inputs as defined in DVI 1.0 specs for Sink devices. It decodes the video stream and outputs 24-bit RGB video data along with the pixel clock and synchronization signals recovered from the TMDS link. More details about its functionality can be found in the documentation

- hls_contrast_stretch_1_0 - The IP interfaces to both Axi-Lite and Axi-Stream in order to process a video stream and control the resolution and the contrast factor. More details about its functionality can be found in the documentation

- hls_gamma_correction_1_0 - The IP interfaces to both Axi-Lite and Axi-Stream in order to process a video stream and control the resolution and the gamma factor. More details about its functionality can be found in the documentation

- hls_saturation_enhance_1_0 - This IP interfaces to both Axi-Lite and Axi-Stream in order to process a video stream and control the resolution and the saturation factor. More details about its functionality can be found in the documentation

- rgb2dpvid_v1_0 - This IP interfaces to an RGB video data bus at its inputs and outputs a video data interface of the Xilinx LogiCORE IP DisplayPort. More details about its functionality can be found in the documentation

- rgb2dvi - This IP interfaces directly to raw transition-minimized differential signaling (TMDS) clock and data channel outputs as defined in DVI 1.0 specs for Source devices. It encodes 24-bit RGB video data along with the pixel clock and synchronization signals. More details about its functionality can be found in the documentation

- rgb2vga_v1_0 - It accepts a Xilinx vid_io input and outputs an independently customizable color depth, properly blanked RGB pixel bus to connect to a VGA DAC. More details about its functionality can be found in the documentation

- usb2device_v1_0 - It provides communication between an AXI Microblaze system and a USB 2.0 Host. More details about its functionality can be found in the documentation

- video_scaler - This IP takes video frames of arbitrary resolution over a slave AXI-Stream interface, resizes them to an arbitrary output resolution and outputs on a master AXI-Stream interface. It has an AXI4-Lite interface for control. More details about its functionality can be found in the documentation

Interfaces

- calib_coef_v1_0 - Digilent Calibration Coefficients port

- pmod_v1_0 - Pmod Interface for Digilent FPGAs

- spi_ctl_v1_0 - Digilent SPI custom control

- tmds_v1_0 - Raw TMDS electrical interface as defined in DVI 1.0