This is an old revision of the document!

Using Github Demos

Overview

Digilent provides several projects through Github that are designed to demonstrate different usages of our FPGA and Zynq boards. This guide will describe how to download and use any of these projects.

At the end of this tutorial you will have your demo project running on your board.

Prerequisites

Hardware

- A Supported Digilent 7-Series FPGA or Zynq Board

- USB Cables

Software

- Xilinx Vivado 2016.X

- Vivado 2016.4 is used in this tutorial

- Digilent Board Support Files

- Follow the wiki guide on how to install Board Support Files for Vivado 2015.X

- Projects Supported by this Tutorial

-

Platform Project Name Uses SDK Wiki Link Github Link Arty Pmod VGA Demo No Internal Link External Link

Important

For further requirements, please review the project's wiki page .

Tutorial

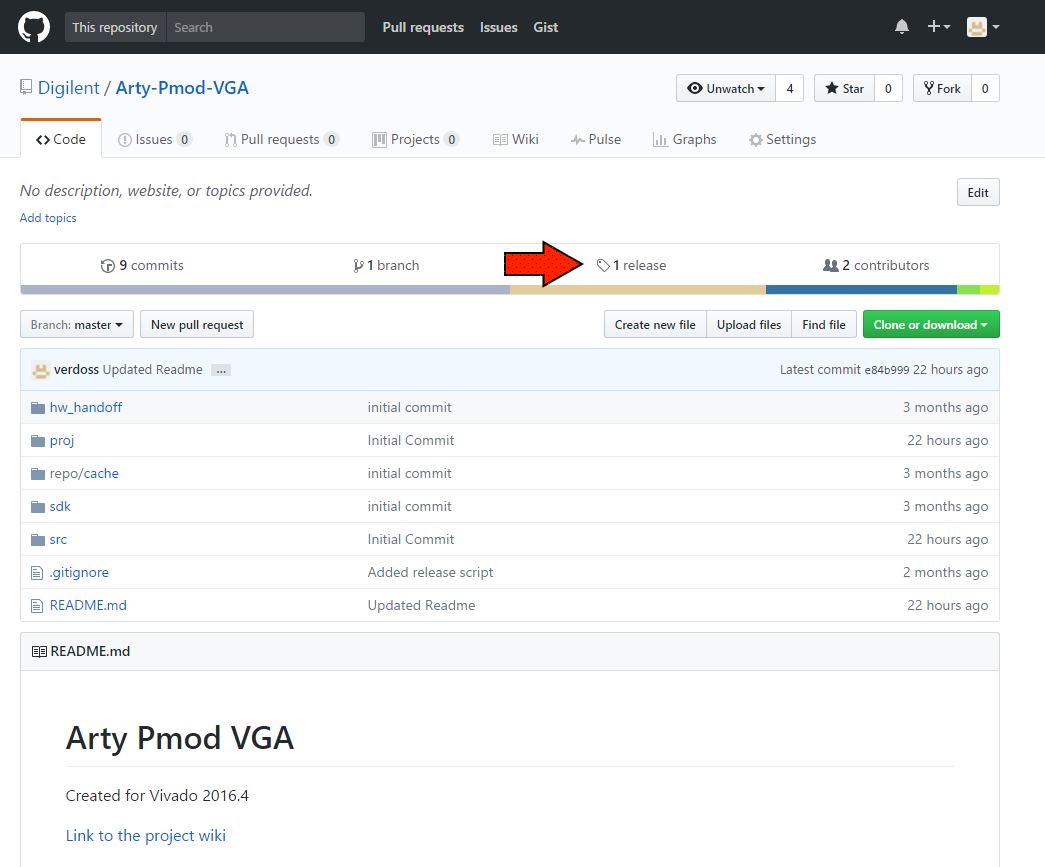

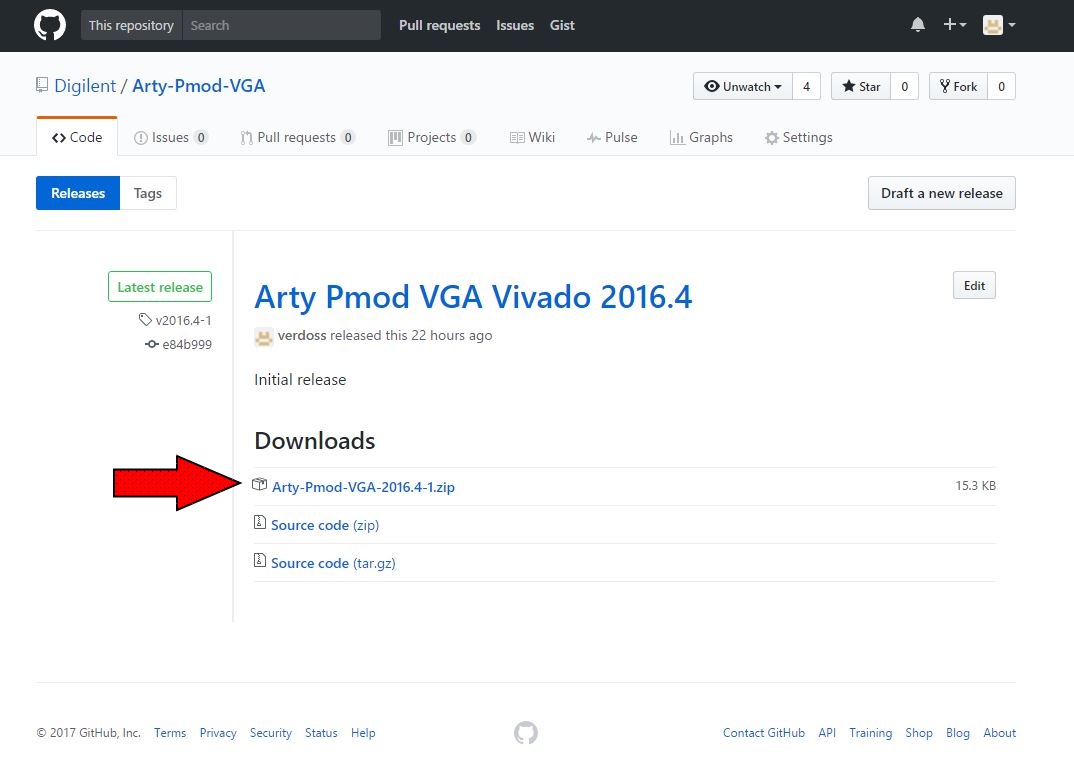

1. Download the Project ZIP from the Digilent Github

1.3) All of the necessary files are included within each project folder, with relative file paths established, so as long as the files aren't moved around within the folder, you can move and run the project from any location.

2. Find the Location of the Tcl Script

3. Create the Project in Vivado

3.3) Enter the command “source ./create_project.tcl”, this will set up the project for you within the proj directory you previously cd'd into.

3.4) The project will now be open in Vivado and you can navigate through the Design Sources subwindow or select Open Block Design in the project flow manager to see how the project hardware works. (Not all projects will have a block design)

4. Generate a Bitstream

4.1) Click Generate Bitstream on the left hand menu towards the bottom. In the “Launch Runs” dialog, make sure Launch runs on local host is selected and click OK. In the “No Implementation Results Available” dialog, click Yes to run synthesis and implementation.

Tip

If your computer has multiple cores, you can increase the number of jobs to make this process faster.

4.2) When this process has finished, which may take a while, in the “Bitstream Generation Completed” dialog, select Open Hardware Manager and click OK. Other interesting options here include “Open Implemented Design” which will show how your project logic will be placed on the FPGA. “View Reports” will show a number of different statistics about your project, including how well it meets timing requirements and what resources of your board will be used.

5. Program your FPGA or Zynq

5.1) Open Hardware Manager

5.2) Open New Target

5.3) Local Server

5.4) Finish

5.5) Program Device

5. Launch Vivado SDK

Export Hardware - Include Bitsream

Launch SDK

6. Compile

Import?

Build All

7. Program the FPGA or Zynq PL

Make sure that your board is turned on and connected to the host PC via both the JTAG USB port and the UART USB port.

On the top toolbar, click the Program FPGA button.

Click Program to program your FPGA with your hardware design.

7. Program the Processor

Select your Pmods project and click the Run As… button. Select Launch on Hardware (System Debugger) and click OK.

- Test

-

Important

Important thing here.

Tip

Use a tip box for tips.