This is an old revision of the document!

Getting Started with Zynq Servers

Overview

This guide will provide a step by step walk-through of creating a Zynq based hardware design using the Vivado IP Integrator that will build over the Getting Started with Zynq guide by making use of the on-board Ethernet port and GPIOs for the Zybo FPGA board.

At the end of this tutorial you will have a comprehensive hardware design for Zybo that makes use of various Hardware ports on the Zybo which are managed by the Zynq Softcore Processor block.

Prerequisites

Hardware

- Digilent's Zybo Development Board and a Micro USB cable for UART communication and JTAG programming

Software

- Xilinx Vivado 2015.X with the SDK package.

Board Support Files

- Zybo Support Files

- These files will describe GPIO interfaces on your board and make it easier to select your board in the initial design setup and add GPIO IP blocks in the block design

- Follow this Wiki guide Vivado Board Files for Digilent 7-Series FPGA Boards on how to install Board Support Files for Vivado 2015.X

Tutorial

General Design Flow

I. Vivado

- Open Vivado and select Zybo board

- Create an new Vivado Project

- Create empty block design workspace inside the new project

- Add required IP blocks using the IP integrator tool and build Hardware Design

- Validate and save block design

- Create HDL system wrapper

- Run design Synthesis and Implementation

- Generate Bit File

- Export Hardware Design including the generated bit stream file to SDK tool

- Launch SDK

Now the Hardware design is exported to the SDK tool. The Vivado to SDK hand-off is done internally through Vivado. We will use SDK to create a Software application that will use the customized board interface data and FPGA hardware configuration by importing the hardware design information from Vivado.

II. SDK

- Create new application project and select default Hello World template

- Program FPGA and run application

1. Creating a New Project

When you first run Vivado this will be the main start window where you can create a new project or open a recent one.

1.1) Click on Create New Project.

1.2) You will be presented with the project creation wizard. Click Next.

1.3) Enter a project name and location the click Next.

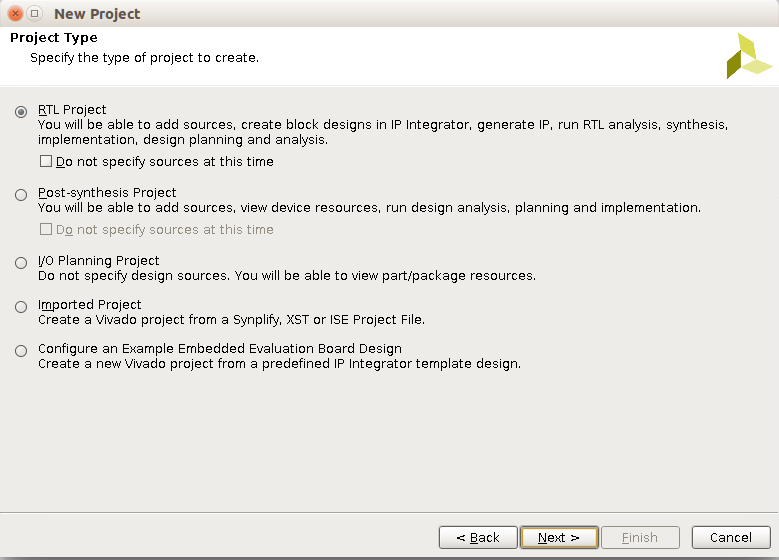

1.4) Select RTL Project and click Next.

1.5) This demo does not use any existing sources, existing IP or constraints. Click through the next three screens.

1.6) Select Boards and select the Zybo board file. Click Next and then Finish.

2. Creating a New Block Design

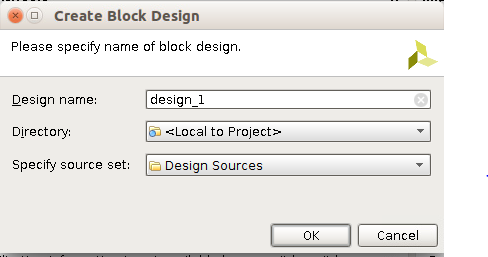

2.1) Once the process has completed, click Create Block Design in the flow navigator.

2.2) Click OK.

2.3) A blank Block Design will open up.

3. Run the Connection Automation Tool

3.1) Click theAdd IP button and search for ZYNQ. Double click on ZYNQ7 Processing System to place the bare Zynq block.

3.2) The connection automation tool will add the required logic blocks for the demo. Select Run Block Automation highlighted in blue.

3.3) Click the Run Block Automation link

3.4) Connect FCLK_CLK0 to M_AXI_GP0_ACLK

4. Generate HDL Wrapper and Validate Design

4.1) SelectValidate Design. This will check for design and connection errors.

4.2) After the design validation step we will proceed with creating a HDL System Wrapper. In the block design window, under the Design Sources tab, right-click on the block diagram file. We labeled it “design_1.bd” and select Create HDL Wrapper.

This will create a top module in VHDL and will allow you to generate a bitstream.

5. Generate the Bitstream

5.1) Click on Generate Bitstream at the bottom of the Flow Navigator. Wait for the process to complete and click OK.

6. Export hardware files for SDK

6.1) Go to file→Export→Export Hardware… Make sure to check the box for Include bitstream then click OK.

7. Launch SDK

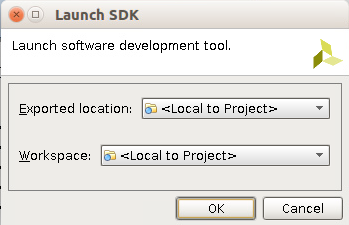

7.1) Go to File→Launch SDK and click OK.

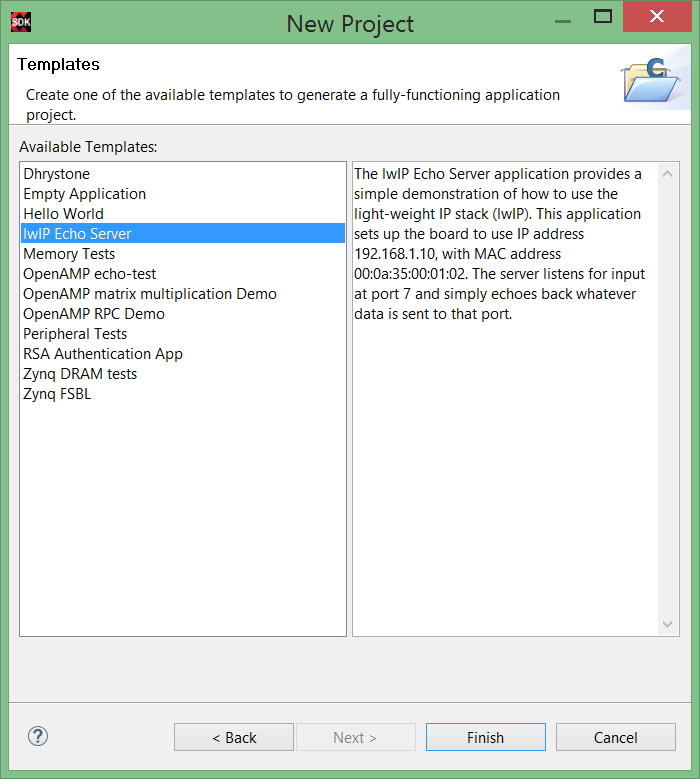

8. Creating New Application Project in SDK

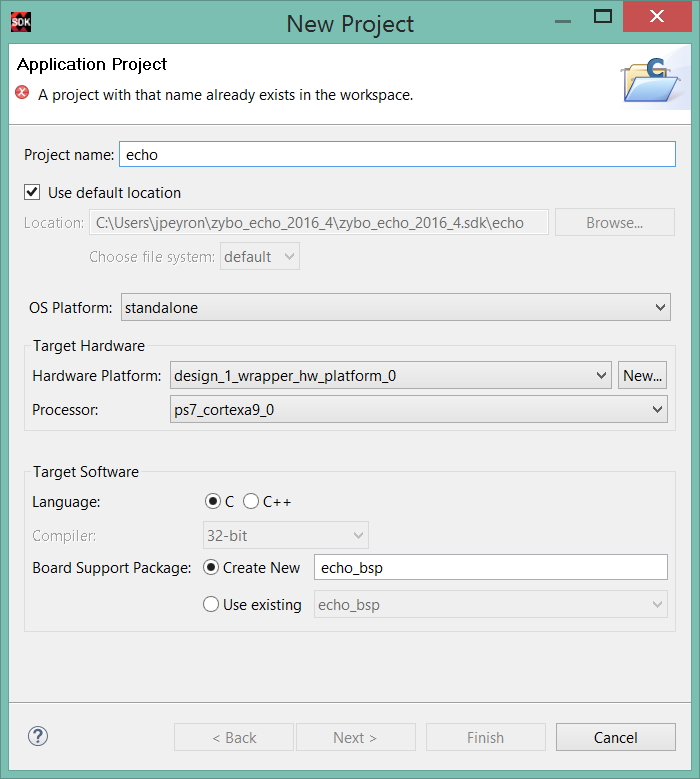

8.1) Go to File→New→Application Project in the main toolbar. A new project window will pop up. Give your SDK project a name that has no empty spaces as shown below. Make sure the Target Hardware is the correct hardware design. In our case, it will be design_1_wrapper_hw_platform_0.

If for example, you also have another hardware design in the Project Explorer window, then you will also see this design name in the Target Hardware drop down selection list.

Since we only have one hardware design design_1_wrapper_hw_platform_0 this will be our target hardware. Select Create New under Board Support Package. The tool will automatically populate the Board Support Package name to match with the give project name. Click Next.

8.3) After completing the previous step, you will see two new folders in the Project Explorer panel. echo which contains all the binaries, .c and .h (Header) files, and echo_bsp which is the board support folder.

echo is our main working source folder. This also contains an important file shown here in the src folder called lscript.ld. This is a Xilinx auto generated linker script file.

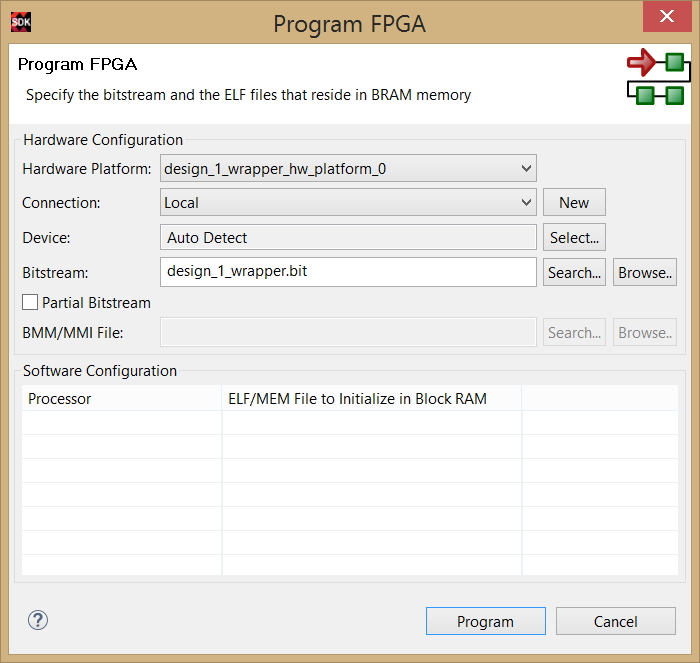

9. Programming FPGA with Bit File

9.1) Make sure that the Zybo is turned on and connected to the host PC via micro USB cable. On the main toolbar, click Xilinx Tools→Program FPGA

Make sure that the Hardware Platform is selected as design_1_wrapper_hw_platform_0.

In the software configuration box, under ELF File to Initialize in Block RAM

Now click on Program.

10. Tera Term Terminal Emulator

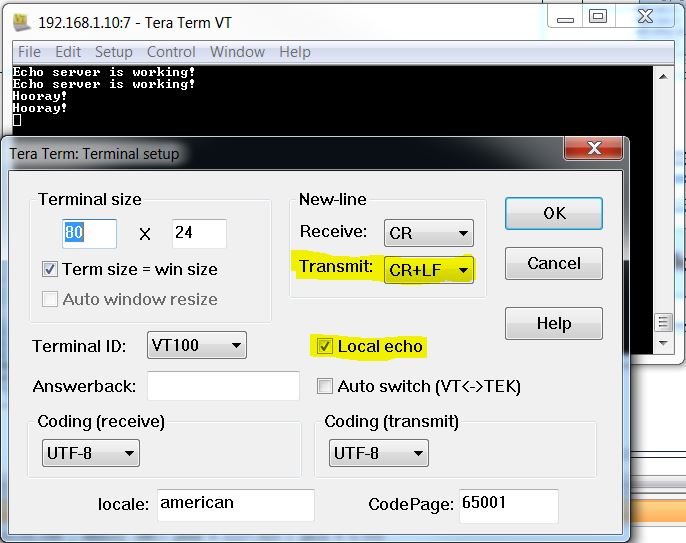

You can use the SDK concsole or other serial terminal. I typically use Tera Term. Refer to this link http://en.wikipedia.org/wiki/Tera_Term to know what Tera Term is. You can download and install Tera Term from this link http://ttssh2.sourceforge.jp/index.html.en

Establish a serial connection with the correct communication port inside Tera Term.

Tera Term will work as a Console by displaying the output.

The serial setup is as shown below.

Go to SDK Run Configurations → Apply and Run.

11. Running the Server

12. Testing the Server with Tera Term

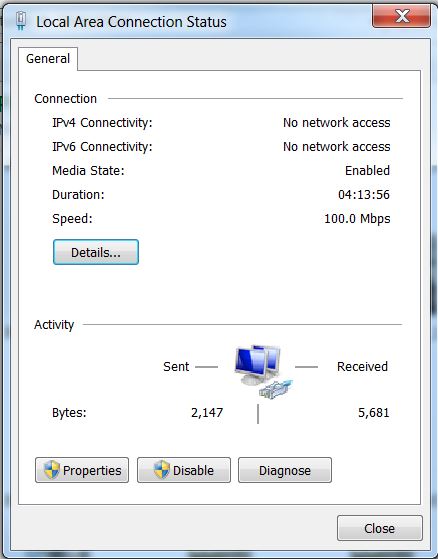

12.1) Connect your PC to your Zybo using an Ethernet cable. If using a router, watch the UART console to find out the IP of the Zybo echo server, and connect to that IP address. Setting up the connection as static is unnecessary.

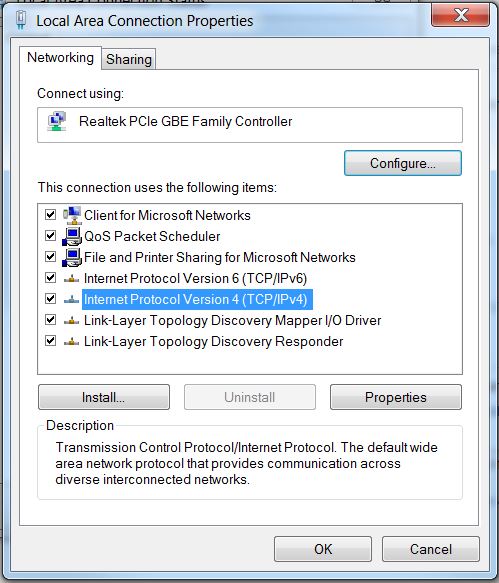

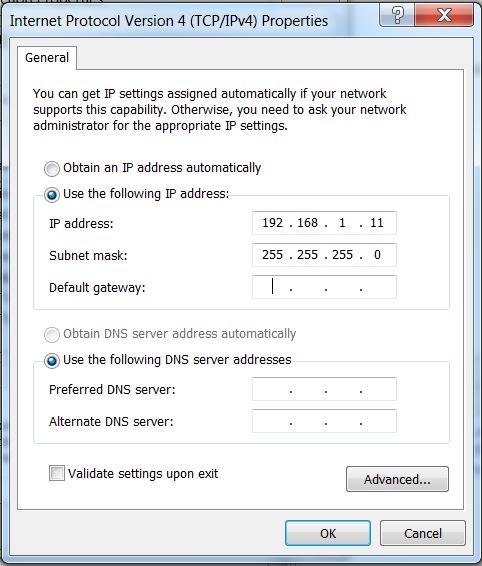

12.2) In order to connect to the echo server directly from your computer, you must set up your Ethernet connection with a static IP address. To do this:

14.2.5) Click the Use the following IP address: bullet and type in an IP address “192.168.1.XX”, where XX is a value between 2 and 255, but not 10. This IP must not be the same as another already on your network. Make sure to click within the Subnet mask field to get the 255.255.255.0 mask to autofill. Click Ok and you will have a static IP address.