This is an old revision of the document!

Arty Z7 Getting started with Zynq

Important!

This guide is obsolete, the updated guide can be found here.

Overview

This guide will provide a step by step walk-through of creating a hardware design using the Vivado IP Integrator for the Arty-Z7 board.

At the end of this tutorial you will have:

- Created a simple hardware design incorporating the on board LEDs,switches and buttons.

- Created a .C project in XIlinx Vivado SDK tying the on board LEDs and buttons together along with sending switch status through the USB-UART using the hardware design shown in the previous step.

Prerequisites

Hardware

- Digilent's Arty-Z7 Development Board and a Micro USB cable for UART communication and JTAG programming

Software

- Xilinx Vivado 2017.X with the SDK package.

Board Support Files

- Arty-Z7 Support Files

- These files will describe GPIO interfaces on your board and make it easier to select your board in the initial design setup and add GPIO IP blocks in the block design

- Follow this Wiki guide Vivado Board Files for Digilent 7-Series FPGA Boards on how to install Board Support Files for Vivado 2015.X

Features Used

| Not Used | Used | |

|---|---|---|

| 2 user switches | X | |

| 2 user LEDs | X | |

| 2 user RGB LEDs | X | |

| 4 user push buttons | X | |

| USB-UART Bridge | X | |

| Micro SD card connector | X | |

| HDMI Sink and HDMI Source | X | |

| PWM mono audio out w/ 3.5mm jack | X | |

| 10/100/1000 Ethernet PHY | X | |

| 512MB 1050Mb/s DDR3 Memory | X | |

| Quad-SPI Flash | X | |

| Two Pmod ports | X | |

| chipKIT connector for XADC signals | X | |

| USB HID Host | X |

General Design Flow

I. Vivado

- Open Vivado and select Arty-Z7 board

- Create an new Vivado Project

- Create empty block design workspace inside the new project

- Add required IP blocks using the IP integrator tool and build Hardware Design

- Validate and save block design

- Create HDL system wrapper

- Run design Synthesis and Implementation

- Generate Bit File

- Export Hardware Design including the generated bit stream file to SDK tool

- Launch SDK

Now the Hardware design is exported to the SDK tool. The Vivado to SDK hand-off is done internally through Vivado. We will use SDK to create a Software application that will use the customized board interface data and FPGA hardware configuration by importing the hardware design information from Vivado.

II. SDK

- Create new application project and select default Hello World template

- Program FPGA and run application

——-

1. Creating a New Project

When you first run Vivado this will be the main start window where you can create a new project or open a recent one.

2. Creating a New Block Design

3. Add the Zynq IP & GPIO Blocks

3.3) Click theAdd IP icon again, this time search for “gpio” and add the AXI GPIO core.

3.4) Double-click on new axi_gpio_0 core that was just added to bring up the customizing window. Under the IP Configuration tab check the Enable Dual Channel box. Click OK.

3.5) Add another GPIO core by repeating step 3.3 but do not enable dual channel.

—–

4. Run the Connection Automation Tool

5. Generate HDL Wrapper and Validate Design

This will create a top module in VHDL or Verilog depending on what language you choose and will allow you to generate a bitstream.

6. Generate the Bitstream

6.1) Click on Generate Bitstream at the bottom of the Flow Navigator.

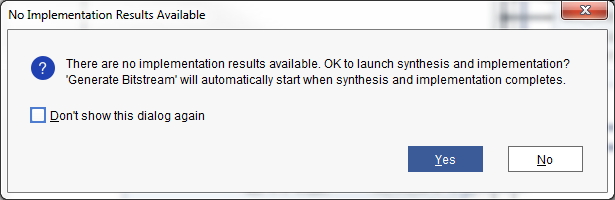

6.2) Next there are a series of popup boxes. On the first popup select save

On the second popup select yes. You can choose to have this not notify you again.

On the last popup choose the max number of jobs allowed if you have no other tasks going on your PC. Otherwise choose the number of jobs based on system needs.

7. Export hardware files for SDK

8. Launch SDK

9. Create a new Hello World Application Project in SDK

10. Creating Our Own Hello World

10.1) Copy and paste the code below into the helloworld.c file.

/*****************************************************

Getting Started Guide for Arty-Z7

This demo displays the status of the buttons on the

LEDs and prints a message to the serial communication

when a switch is on.

Terminal Settings:

-Baud: 115200

-Data bits: 8

-Parity: no

-Stop bits: 1

9/21/17: Created by JPEYRON

****************************************************/

#include <stdio.h>

#include "platform.h"

#include <xgpio.h>

#include "xparameters.h"

#include "sleep.h"

int main()

{

XGpio input, output;

int button_data = 0;

int switch_data = 0;

XGpio_Initialize(&input, XPAR_AXI_GPIO_0_DEVICE_ID); //initialize input XGpio variable

XGpio_Initialize(&output, XPAR_AXI_GPIO_1_DEVICE_ID); //initialize output XGpio variable

XGpio_SetDataDirection(&input, 1, 0xF); //set first channel tristate buffer to input

XGpio_SetDataDirection(&input, 2, 0xF); //set second channel tristate buffer to input

XGpio_SetDataDirection(&output, 1, 0x0); //set first channel tristate buffer to output

init_platform();

while(1){

button_data = XGpio_DiscreteRead(&input, 1); //get switch data

XGpio_DiscreteWrite(&output, 1, button_data); //write switch data to the LEDs

switch_data = XGpio_DiscreteRead(&input, 2); //get button data

//print message dependent on whether one or more buttons are pressed

if(switch_data == 0b00){} //do nothing

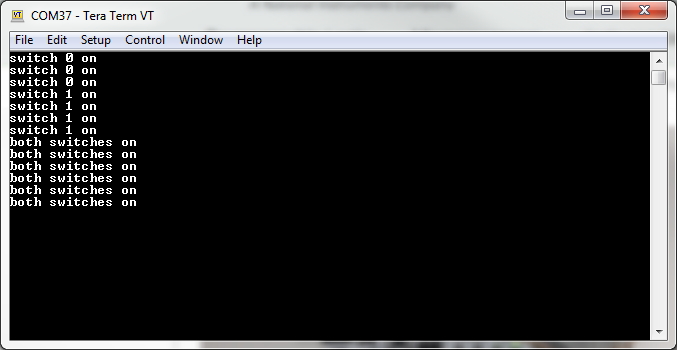

else if(switch_data == 0b01)

xil_printf("switch 0 on\n\r");

else if(switch_data == 0b10)

xil_printf("switch 1 on\n\r");

else

xil_printf("both switches on\n\r");

usleep(200000); //delay

}

cleanup_platform();

return 0;

}

11. Run the Project

11.1) Make sure that the Arty-Z7 is connected to the host PC via the UART USB Port and that JP4 is set to JTAG. To program the FPGA, on the top toolbar, click theProgram FPGA button.

11.2) Save the project. The project will automatically build.

11.3) Right click the Getting_started_with_zynq directory and select run as → Launch on Hardware(System Debugger).

11.4) The demo will be running on the Arty-Z7. Try playing around with the (labeled BTN0-BTN3). Pressing each button should light its respective LED. Also over the serial port, the 2 switches (labeled SW0-SW1) will produce the message “switch x on” or “both switches on”.

11.5) Tera Term or any serial terminal will work as a Console for displaying the output of the BTN's.

Set up the terminal as: