This is an old revision of the document!

Arty Pmod VGA Demo

Overview

Features Used

| Not Used | Used | |

|---|---|---|

| 4 User Switches | X | |

| 4 User LEDs | X | |

| 4 User RGB LEDSs | X | |

| 4 User Push Buttons | X | |

| 4 Pmod Connectors | X | |

| XADC Analog Input | X | |

| USB-UART Bridge | X | |

| Serial Flash for Application Data | X |

Description

This simple VGA Demo project demonstrates usage of a Pmod VGA connected to the Arty's Pmod ports. The behavior is as follows:

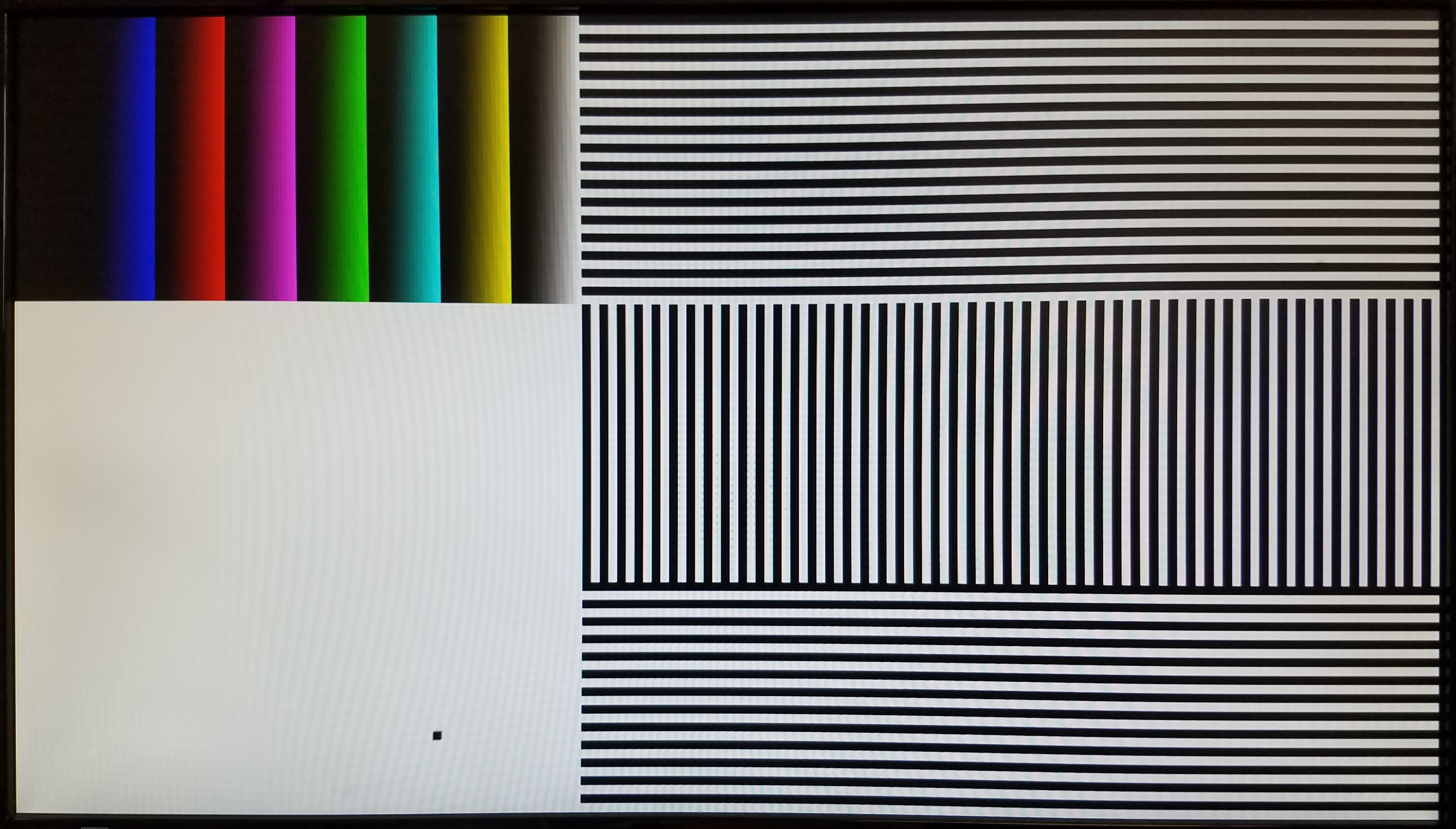

- A bouncing box and black, white, and multiple colors of bars are displayed on a connected VGA monitor.

- The Pmod VGA is controlled by the Arty through Pmod ports JB and JC.

- The screen resolution is configurable through HDL code.

Prerequisites

Hardware

- Arty FPGA board

- Pmod VGA

- Micro-USB cable

- VGA monitor and cable

Software

- Vivado Design Suite 2016.4

- Newer versions can be used, but the procedure may vary slightly

- Digilent Board Support Files for Vivado

- Follow the Vivado Board Files for Digilent 7-Series FPGA Boards guide on how to install Board Support Files for Vivado.

Downloads

How to...

1. Program the Board

1.1) Follow the Using Digilent Github Demos Tutorial. This is an HDL design project, and as such does not support Vivado SDK, select the tutoral options appropriate for a Vivado-only design.

1.2) Once you have generated your bit file, make sure that you have your Pmod VGA plugged into your Arty's Pmod ports JB and JC. Use a VGA cable to connect the Pmod VGA to your monitor's VGA port. Return to the Github Projects Tutorial to finish programming your board.

2. Run the Project

This portion will help you run the demo and observe all its features.

2.2) Changing the resolution

You may want to change the display resolution if your VGA monitor does not support 1080p, or you want to modify the demo for a specific application.

To select a different display resolution, select the appropriate set of Sync Generation constants for your target resolution from the list starting at line 47 of top.vhd. Uncomment the ten corresponding constants, FRAME_WIDTH through V_POL, and comment out the default versions of those same constants. The default resolution is 1920×1080 @ 60Hz.

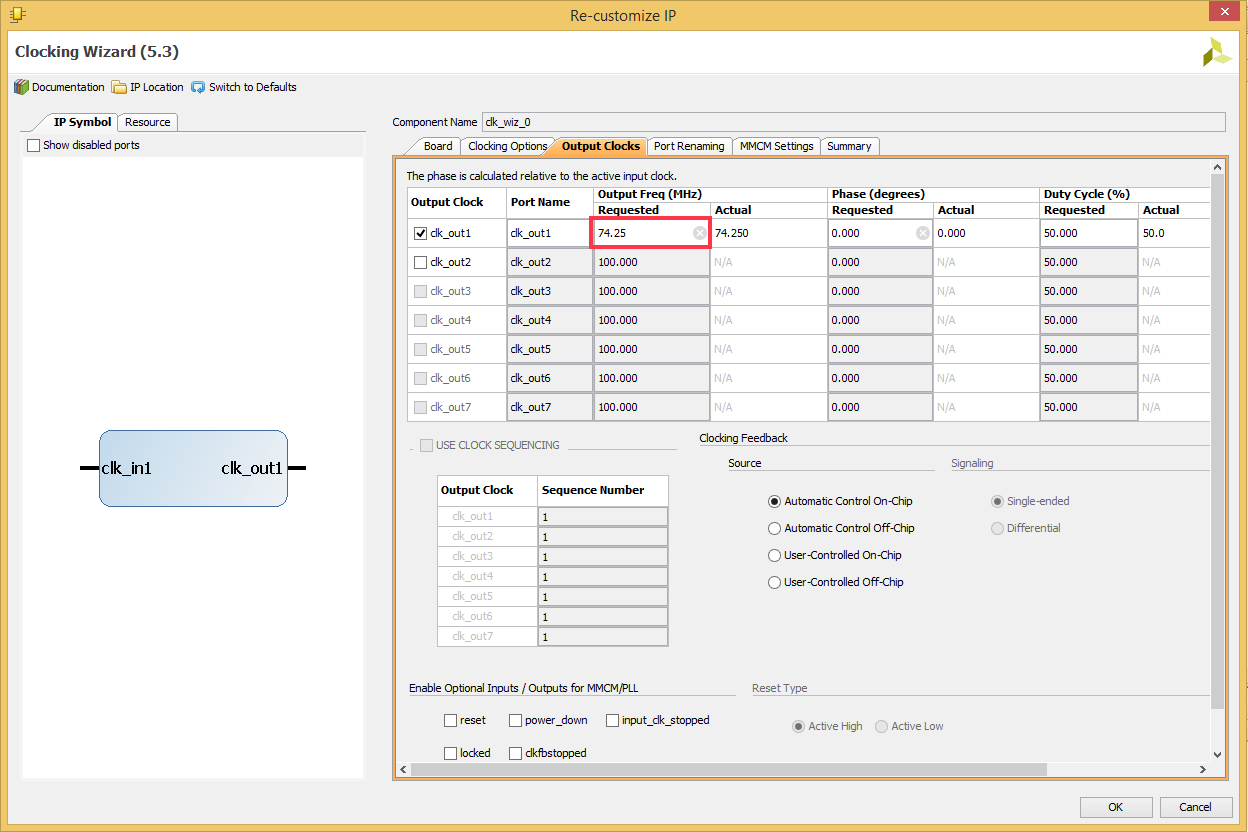

Next select Project Manager in the Flow Navigator. In the Hierarchy tab of the Sources box, expand top under Design Sources and double click on clk_div_inst. Change the clk_out1 Requested frequency - circled in red below - to the required pxl_clk frequency specified in the selected resolution's Sync Generation comment block. Select Ok, then Generate in the Generate Output Products dialog that pops up. To reprogram your board with the new hardware, return to Step 2.