This is an old revision of the document!

Cmod A7 XADC Demo

Overview

Features Used

| Not Used | Used | |

|---|---|---|

| 2 user LEDs | X | |

| 1 tri-color LEDs | X | |

| 2 User Push Buttons | X | |

| 48 GPIO Pins | X | |

| 1 Pmod port | X | |

| Pins for XADC signals | X | |

| USB-UART Bridge | X | |

| 512 kB SRAM | X |

Description

This simple XADC demo is a verilog project made to demonstrate the ADC functionality of the Cmod-A7

- The RGB LED brightens the RED LED when the read voltage goes up.

- When BTN1 is pressed, the demo switches which xadc pin to read from.

This demo uses XADC ports 4 and 12 since they are the channels connected to pin 15 and 16. This can be seen in the schematic below.

Prerequisites

Skills

- Basic familiarity with Vivado

- This experience can be found by walking through our “Getting Started with Vivado” guide

Hardware

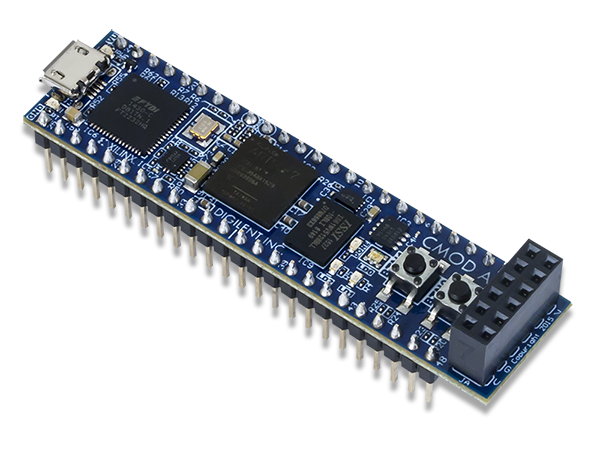

- Cmod A7 FPGA board

- Micro-USB cable

- Breadboard

- Resistors

- Wire

Software

- Vivado Design Suite 2015.X

- Newer/older versions can be used, but the procedure may vary slightly

Downloads

Cmod A7 Support Repository – GIT Repo

How to...

1. Generate the Project

1.1) Download the repository linked in the download section and place it in the location of your choosing.

1.2) Generate the XADC project in the Projects folder by following this guide before continuing: How to Generate a Project from Digilent's Github

2. Build the Project

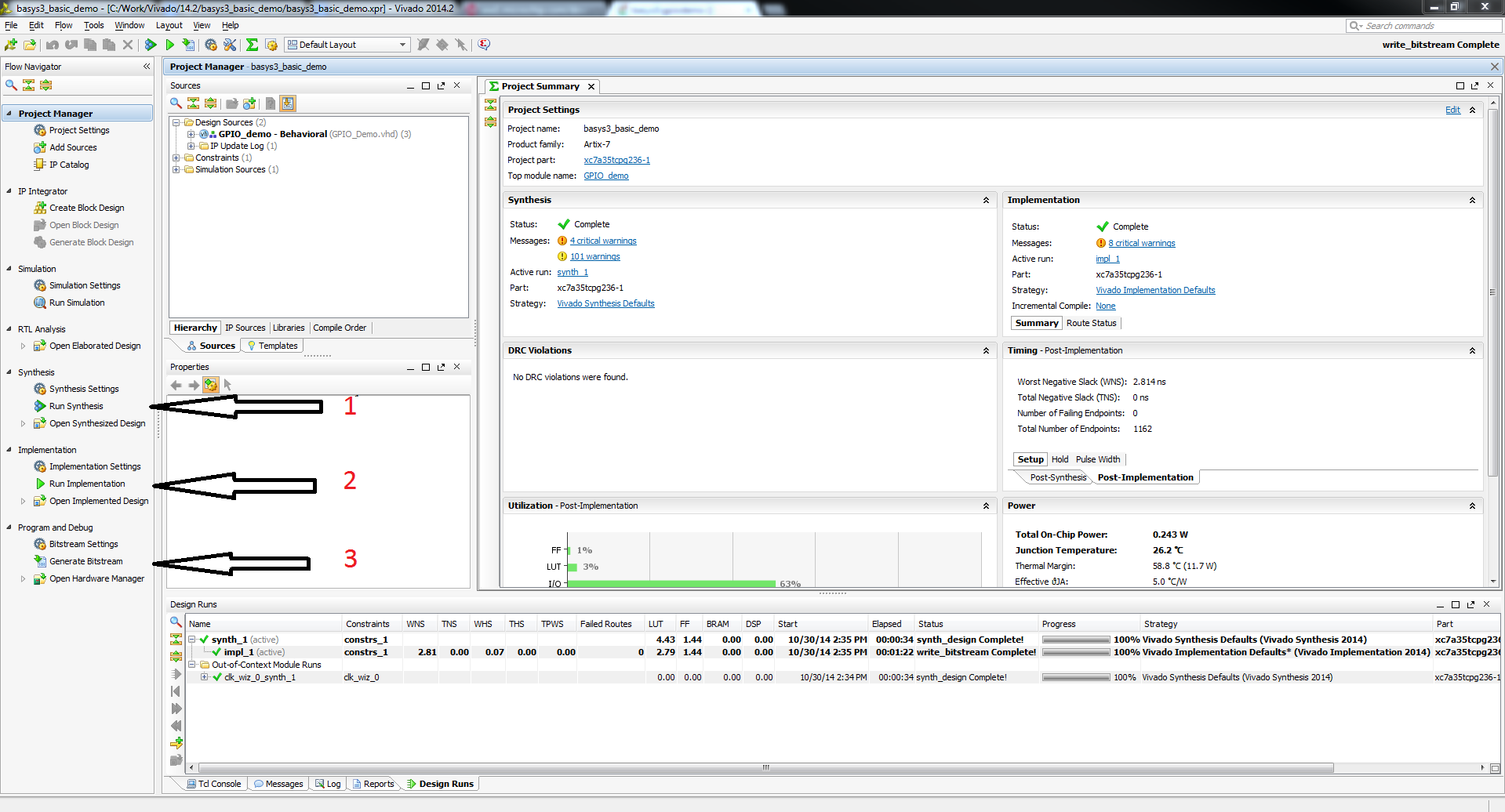

2.1) Click Generate Bitstream on the left hand menu towards the bottom. Vivado will run through both Run Synthesis and Run Implementation before it generates the bitstream automatically.

Note: If you want, you can click each step by itself in the order of Run Synthesis, Run Implementation and then Generate Bitstream.

3. Program the Board

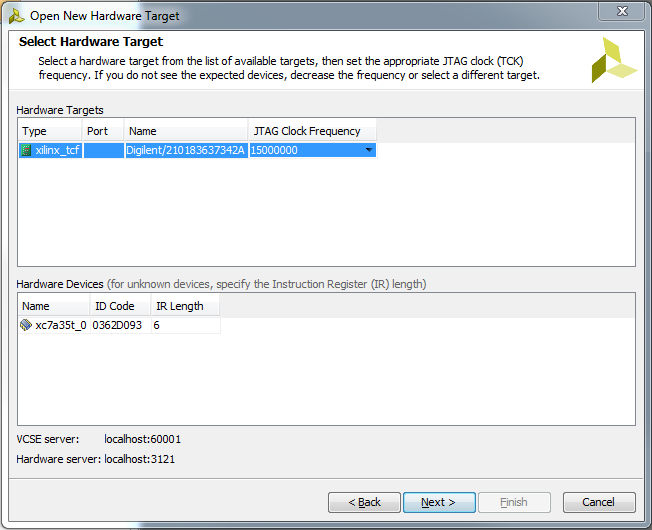

3.2) Click program to load the project onto your Cmod A7.

4. Run the Project

This portion will help you run the demo and observe all its features.