At this point in reading the blog and going through the Learn material, you might realize that there is a lot of FPGA code. It doesn’t look like C, it doesn’t look like Java…what is it?

When learning FPGA design, there are two languages to choose from, Verilog or VHDL. They are called HDLs, or hardware design languages. Unlike a language like C, where they define what you want the circuit to do, HDLs define how the hardware needs to be configured. Now, it’s not exactly as clear as that, as you can code behaviorally or structurally in HDL, but that’s the main idea.

So if you want to program FPGAs, which do you use?

I use Verilog, but that’s only because that’s what I was taught. The languages are very close, so once you learn one it’s not to hard to learn the other. Thus, picking one to learn first is not that big of a decision. But if you are concerned about it, the general consensus is that it is much easier to learn VHDL and then learn Verilog, because VHDL is the harder language to learn. However if you’ve already learned Verilog, I wouldn’t be too discouraged.

They also say that is easier to Learn C, then C++, then Java, but I did it in the reverse order and it wasn’t too bad. Another consideration is that in most industries other than defense, it is more common to use Verilog, so if you know what industry you want to work in, you could learn the one that they use.

The differences in usage and the differences in the languages stem from the history of their creation. VHDL was written as a description language, whereas Verilog was written as a hardware modeling language. As a result, VHDL is a strongly typed, verbose, deterministic language. Verilog, being the opposite in terms of its features, looks similar to C code, which is why it is often easier to learn.

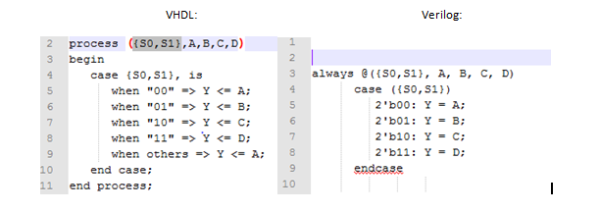

Here is an example of both languages.

- If you are interested in learning more about either language, check out our Learn module and this forum post.

- If you want to learn more about the differences between Verilog and VHDL, check out our in depth comparison page.

- Check out more options when it comes to debugging FPGA designs.

Are you ready to unleash your creativity and dive into the world of digital design? Explore the endless possibilities with Digilent FPGA boards and bring your ideas to life!

Even though for smaller examples VHDL and Verilog look kinda similar, they follow completely different philosophies (as you stated). Thats what makes changing between them so difficult. The moment you understand one language means you are familiar with its underlying philosophy and follow its metaphors and design strategies. Then, when you change, you want to apply these to the new language – and it will fail. So this means to unlearn, and start from anew.

OTOH, having mastered both probably means that you get better in both since you start applying the e.g. the good parts of VHDL in Verilog (and vice versa).

i want to join you

great perspective, loved the way you explained

In verilog inside always block , assignation has to be “<= "(non blocking ).