With the intense tune of Eye of the Tiger playing in the background, it is time to for this showdown to begin. In the left corner we have Verilog. Born in 1984, it didn’t make it to the big scene until 1995. In the right corner we have VHDL, the language created by the US Department of Defense in the 1980’s.

Many people have different opinions on which language is better, but it really comes down to which language you prefer. I should also mention that there is of course System Verilog, but it is very closely related to Verilog so we’ll just leave that for another day. Let’s take a look at these languages and see what the differences are (though the Nexys A7, Cmod A7, and Cmod S7 all support both languages).

VHDL stands for VHSIC Hardware Description Language and VHSIC stands for Very High Speed Integrated Circuit. So on the whole VHDL actually stands for Very High Speed Integrated Circuit Hardware Description Language. Now, that’s a mouthful if I ever saw one! One of the key features of VHDL is that it is a strongly typed language, which means that each data type (integer, character, or etc.) has been predefined by the language itself. All values or variables defined in this language must be described by one of the data types.

VHDL is more verbose than Verilog and it is also has a non-C like syntax. With VHDL, you have a higher chance of writing more lines of code. VHDL can also just seem more natural to use at times. When you’re coding a program with VHDL, it can seem to flow better. But maybe that’s just my personal opinion.

In Verilog, the language is more compact, as the Verilog language is more of a hardware modeling language. You will end up typing few lines of code and it draws similarities to the C language. Verilog has a better grasp on hardware modeling, but has a lower level of programming constructs. Verilog is not as verbose as VHDL so that’s why it’s more compact. All in all, Verilog is pretty different from VHDL. There are some similarities, but they are overshadowed by their differences.

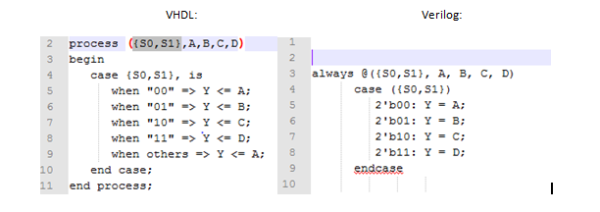

Looking at this example code, we can compare at the how a MUX can be programmed through VHDL and Verilog.

The layout of these programs are very similar; you can reasonably follow what each version of the code is doing. The VHDL version is longer then the Verilog, but it can be understood better.

The last match of this competition is something that can’t be decided easily… it’s the personal preference challenge. This rides on the readers. Weigh in on why you like each programming language, and which one you prefer the most. This is a good opportunity to share some insight on to what beginners should look out for when starting to pick up VHDL or Verilog. If you want to see either language in action, check out some of the learn projects we have on VHDL and Verilog!

Also check out some of our popular projects that use each language. Kaitlyn, a longtime supporter of Verilog details on Instructables some of the awesome things you can do with this powerful tool.

This includes controlling servos on your FPGA! Here she demonstrates how she used the Basys 3 and Verilog to control the motion required for the Claw Game Demo.

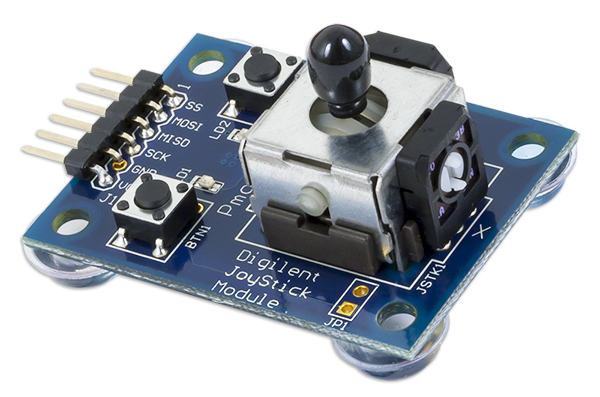

However despite a strong showing from Verilog, VHDL is not so quick to be outdone. Here you can see it in action being used to program the popular PmodJSTK.

This Pmod can then be used for a variety of applications…some even battle-related.

Check out more on the PmodJSTK powered Jouster here!

I was a little confused at first when I read your statement that while you are using VHDL you will have a tendency to write more lines of code but have it seem to flow better since that’s somewhat counter intuitive–instead of being quick and to the point, being long-winded is better?

But knowing that the reverse tends to be true (more lines of code equating to more clarity) for coding and looking that the VHDL to Verilog comparison for a MUX, I can definitely see how the VHDL makes a little more sense, even to the untrained eye (at least I think it does).

hey,

i am my self mostly programming in VHDL.

I would like to point out that the MUX example showed in the article, in Verilog can be very similar to VHDL only by adding 2 more lines that are not most in the example, BUT CAN BE(!!)

always@(…)

begin//the first line, like ‘begin’ in VHDL

.

.

.

end // like ‘end process’ in VHDL.

For what it’s worth because I haven’t touched fpgas for over 15years, VHDL is much more natural as a description language. Also it is easier to “think” in VHDL.

VHDL is far superior to verilog. Verilog is a pathetic hack. And System Verilog is a system level hack. Tried very hard to look like VHDL and failed miserably.

Hi,

thanks for the article.

You might also want to read the article from Mr Gaisler called ‘A structured VHDL design method’

(http://www.gaisler.com/doc/vhdl2proc.pdf)

Mr Gaisler is not comparing the two languages, rather proposing a design methods compared to ‘dataflow’ design for VHDL which is interesting.

Kind regards,

LS

I have used both. I am one of the few who prefers VHDL over verilog. VHDL provides more in when you are creating generic designs compared to Verilog. Please don’t argue on this point because it is a fact. Verilog has some strange quirks that individual vendors try to correct in their implementations. VHDL is better defined and you are less likely to get bitten because you understood something wrong. It just is better defined than Verilog. In fact Systemverilog was created to make Verilog like VHDL. Instead SystemVerilog is a hodge-podge mess.

In the mux example, in Verilog you should write “always @*”. This gives you two things:

1. The inputs to the process are implicit and allows the tools to find them. No more risk of missing stating an input causing latches.

2. You indicate to the tool(s) that the process is combinational. This makes it easier for the tool to find problems and warn you.

This concept was further developed in SystemVerilog into the “always_comb” and “always_ff” statements.

Since you are talking about syntax. It might be worth pointing out that VHDL is case insensitive. Which makes it the more weirder that it is basically a standard in VHDL to write statements in all capital letters. This makes the code harder to read.

Fix your VHDL example code.

VHDL does not have {A, B} syntax. In the process sensitivity list you can use just (S0, S1, A, B, C, D).

The concatenation would look like S0 & S1. However, you cannot use it in the case statement. Create a variable before, say S, and assign it the value S := S0 & S1. Then do “case S is”.

We have a reference app that provides all the keywords of both VHDL and Verilog, notes the equivalent in the other language (when they exist), and gives a simple usage example. http://www.squishlogic.com/VHDLRef/

I have to completely disagree that VHDL reads better than Verilog in your MUX example. There is double the punctuation.

As someone having to learn VHDL coming from SystemVerilog, VHDL syntax is just silly and absurd. Perhaps I just have more experience in SV and C, but the way SV modules are constructed just make more sense to me. Something being more verbose does NOT make it easier for me to understand. I prefer compact designs.