Welcome back to the Digilent blog!

So you’ve heard about FPGAs and learned that you need to download Vivado, so you found a great guide on how to install Vivado, booted it up, and … now what? If this sounds more familiar than you would like to admit, then you’ve come to the right place. We’re going to walk though a series of posts over the next few days to help you get up and running with a new Vivado project including: getting any extra files you need ready to go (the post you’re reading right now!), initially setting up a Verilog project in Vivado, making changes to our Verilog project and XDC file to have it work on our FPGA, and finally generating the bitstream that we will use to program our FPGA. Let’s get started!

While it would be nice to think that we can simply just write up an FPGA program and configure our board with it and then move on to the next program, FPGAs are complex enough that it is a good idea to add in some pre-made board files to help smooth out the programming process. I will be using Digilent’s Arty throughout the duration of this tutorial series and Verilog as my FPGA programming language of choice as well as the 2016.4 WebPACK edition of Xilinx’s Vivado Design Suite.

The two files we will be looking for is the Arty XDC (Xilinx Design constraints) file and the Arty board file. The XDC file is used by Vivado to associate the names of the inputs and outputs we “create” in our Verilog code to actual pins on the FPGA chip. The board file is used to group different sets of pins on the FPGA together so that they can be readily used when configuring various IP blocks; we won’t be using any IP blocks in this tutorial, but it’s nice to already have the board file installed for the future (and makes it much easier to tell Vivado which FPGA we are working with when we are initially creating a project).

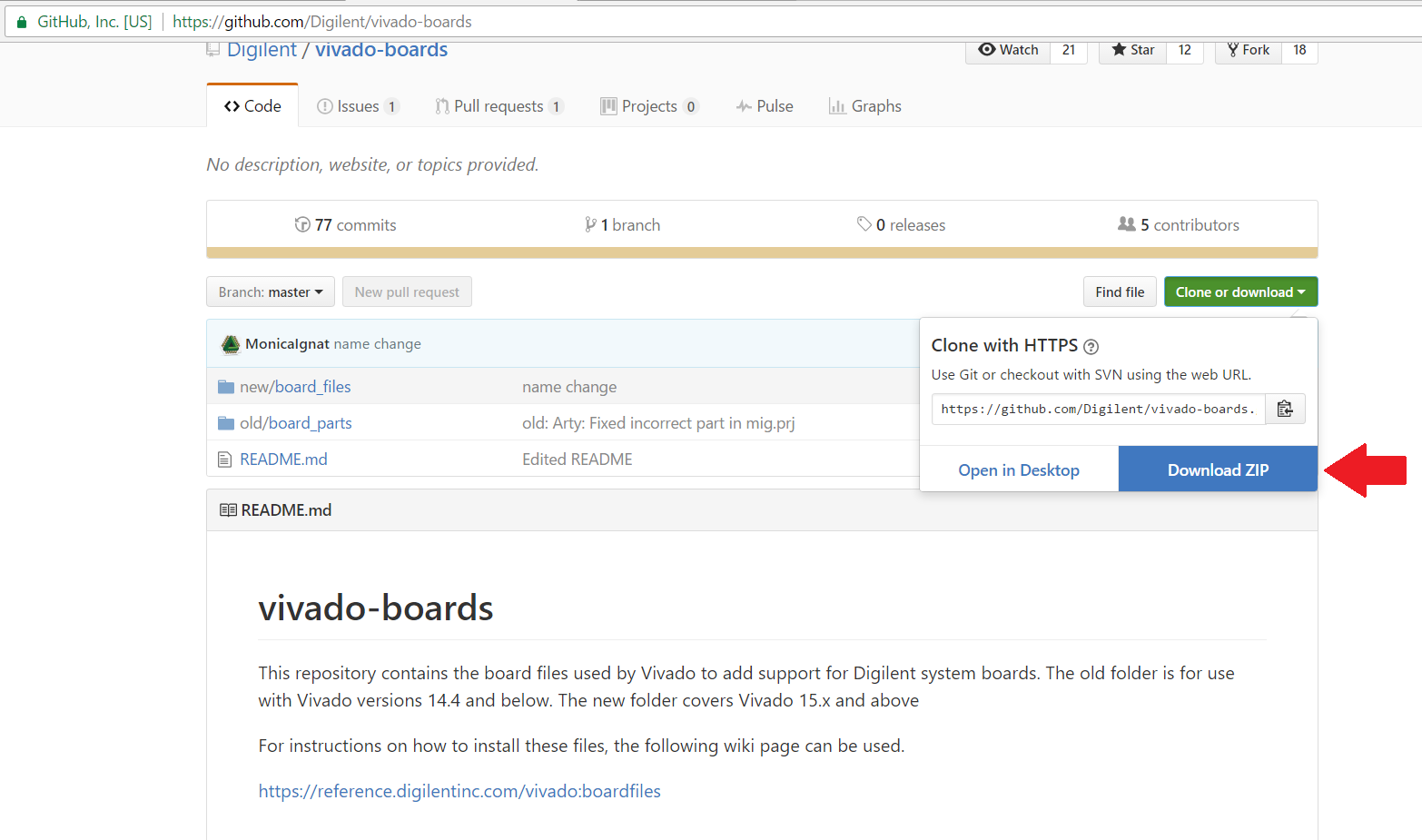

To get the Arty board file, go ahead and download the Digilent board files from the Digilent GitHub account (at the direct download link or view the board files natively in GitHub here). Within the board files .zip folder, you’ll want to extract the “Arty” folder (and everything inside it) to the board_files folder that is inside of the Xilinx directory which you already have installed. On a Windows system, the default location for this board_files folder is C:\Xilinx\Vivado\2016.4\data\boards\board_files; copy the whole “Arty” folder structure into this folder.

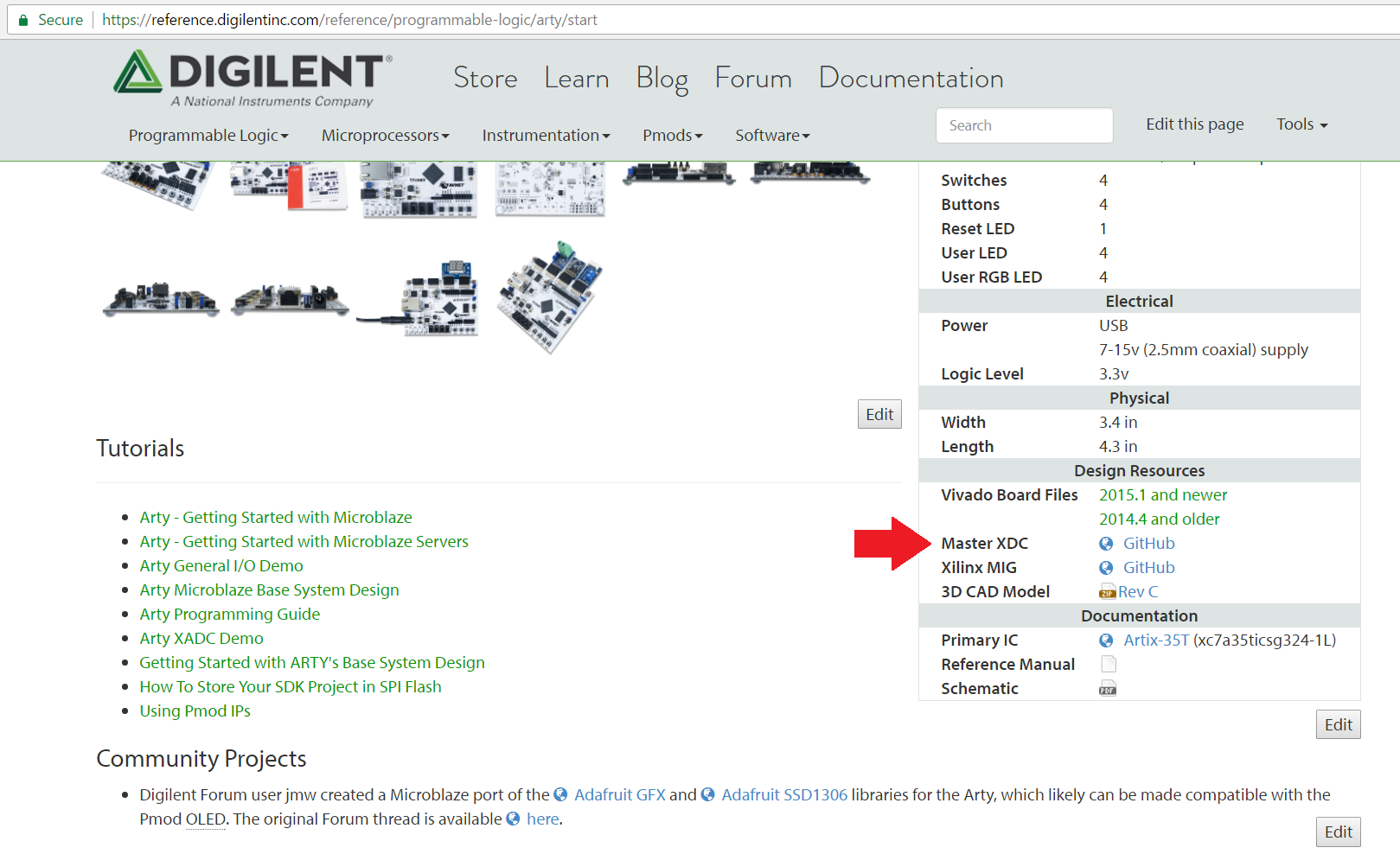

Next, we’ll want to get the XDC file for the Arty so that way we can inform Vivado what physical pins we wish to use with our project. A master XDC file for the Arty (and all of Digilent’s FPGA boards) can be found in their respective Resource Centers on our Wiki. The Arty Resource Center is here, with the Master XDC file available in the box on the right hand side of the screen underneath “Design Resources”. Once you have downloaded the Master XDC file, save it somewhere to your computer where you can easily find it again since we’ll need to be able to tell Vivado where to find the file when we create our project.

This should be enough to get you started, and stay tuned for the next post in this tutorial series! Additionally check out our Wiki for more resources on this project.

Read the rest of the series through the links below:

Creating and Programming our First FPGA Project Part 2: Initial Project Creation

Creating and Programming our First FPGA Project Part 3: Modifying the Project

Creating and Programming our First FPGA Project Part 4: Final Steps

2 Comments on “Creating and Programming our First FPGA Project Part 1 – Getting the Extra Files Ready”