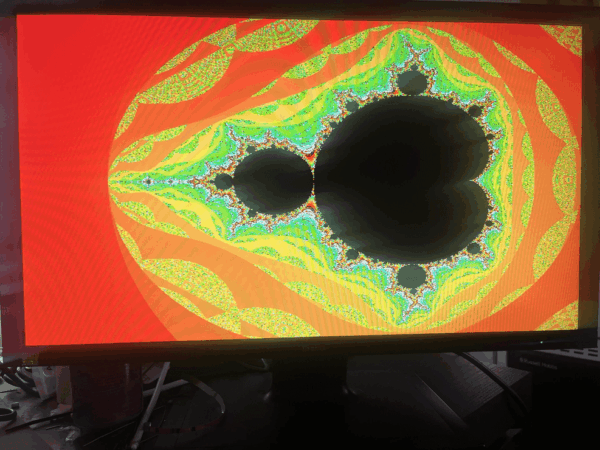

This Mandelbrot set renderer was created by Conrad, who shared the project on GitHub (username conradSZY05). Built for the Digilent Basys 3, the design uses VHDL and Xilinx Vivado to generate a real-time fractal visualization with VGA output.

The project is a complete, hardware-based implementation that brings together video timing, mathematical computation, and FPGA design in a single, working system. It serves as a practical reference for anyone interested in graphics or visualization on the Basys 3.

What the Project Does

The design implements a Mandelbrot set renderer entirely in programmable logic. It computes fractal data in real time and outputs the result directly to a VGA display. All functionality is written in VHDL and synthesized using Xilinx Vivado, targeting the Artix‑7 FPGA on the Basys 3.

In addition to VGA video output, the design includes UART support, enabling serial communication with a host system. This allows interaction or configuration while keeping the rendering and display pipeline fully hardware-driven.

The repository includes source files and documentation that describe the project structure and tool requirements, making it possible for other users to reproduce the implementation as provided.

Why This Design Is a Useful Reference

The Mandelbrot set is well suited to FPGA implementation due to its iterative structure and the independence of individual pixel calculations. These characteristics align naturally with the parallel and pipelined nature of FPGA logic.

As a reference project, this design is valuable because it combines several foundational concepts into a single, working system:

- VGA timing and signal generation

- Fixed-point numerical computation

- Real-time pixel-level processing

- UART integration alongside video logic

Rather than presenting these topics in isolation, the project shows how they can be integrated into a cohesive hardware application.

Target Platform: Basys 3

This project targets the Digilent Basys 3, a widely used FPGA board in academic and learning-focused environments. The Artix‑7 FPGA provides sufficient logic resources for both fractal computation and video control, while the onboard VGA connector allows direct connection to a display without additional hardware.

Because the Basys 3 is commonly used in coursework and labs, this project aligns well with existing learning workflows supported by Digilent.

Development Tools and Implementation Approach

The design is implemented using:

- VHDL for all RTL logic

- Xilinx Vivado for synthesis, implementation, and bitstream generation

- UART for serial communication

- VGA for real-time video output

Screen coordinates are translated into points in the complex plane, and each point is evaluated iteratively to determine divergence. The results are mapped directly to the VGA output, with all timing and control logic generated on the FPGA.

Using This Project as a Learning Resource

Because the design is complete and self-contained, it can be used as a reference by anyone looking to understand how mathematical visualization can be implemented on an FPGA. It is especially relevant for students, educators, and FPGA developers who want to explore video output and computation-heavy designs without introducing a processor subsystem.

The project remains the original work of its creator. Digilent is featuring it to highlight how community-built designs can serve as practical learning references when paired with accessible FPGA hardware.

Project Repository

The full source code and documentation are available on GitHub:

https://github.com/conradSZY05/mandelbrot_rend

This project really highlights the power of FPGAs for computationally intensive tasks like rendering fractals. It’s fascinating to see how the Basys 3 can handle such complex calculations in real-time, and the step-by-step approach makes it accessible for others to build upon. Thanks for sharing this insightful reference implementation.

Congrats on a fun project that you have documented well.

I did a similar project. See github under user “delhatch” project “Pure_Mandel”

Nice job!