Welcome back to the Digilent blog!

So you’ve heard about FPGAs and learned that you need to download Vivado. You may have even found a great guide on how to install Vivado, booted it up, got the extra files that you need, went through the initial project creation in Vivado, modified the project to suit our FPGA, and … now what? If this sounds more familiar than you would like to admit, then you’ve come to the right place. We’ve done several posts to help you get up and running with a new Vivado project including: getting any extra files you need ready to go (available here), initially setting up a Verilog project in Vivado (available here), making changes to our Verilog project and XDC file to have it work on our FPGA (available here), and finally our last post on generating the bitstream that we will use to program our FPGA (the post you’re reading right now!). Let’s get started!

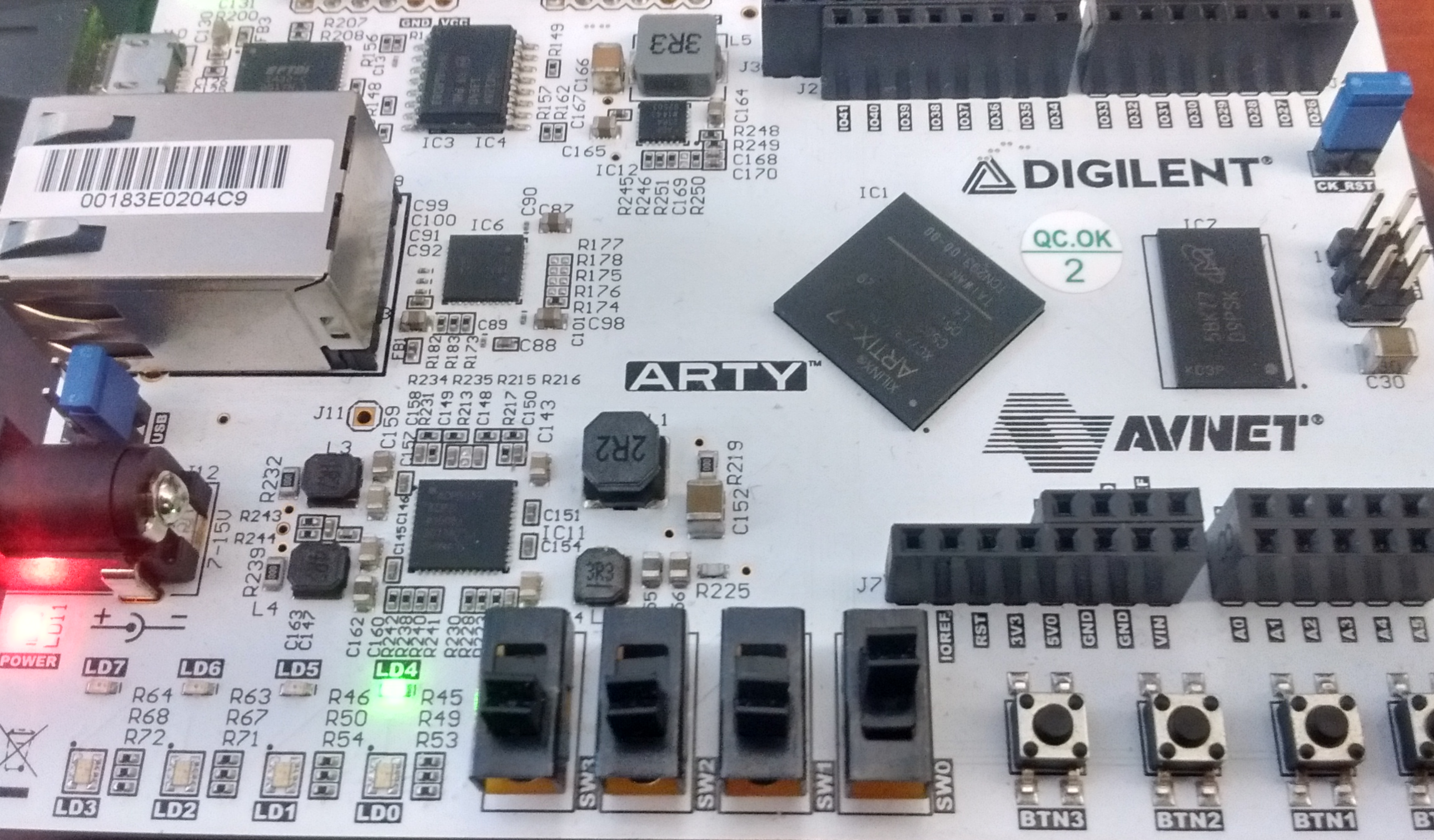

While it would be nice to think that we can simply just write up an FPGA program and configure our board with it and move on to the next program, FPGAs are complex enough that it is a good idea to add in some pre-made board files to help smooth out the programming process. I will be using Digilent’s Arty throughout the duration of this tutorial series and Verilog as my FPGA programming language of choice and the 2016.4 WebPACK edition of Xilinx’s Vivado Design Suite, though boards like the Basys 3, Nexys A7, Cmod A7, Cmod S7, and Arty S7 will also work.

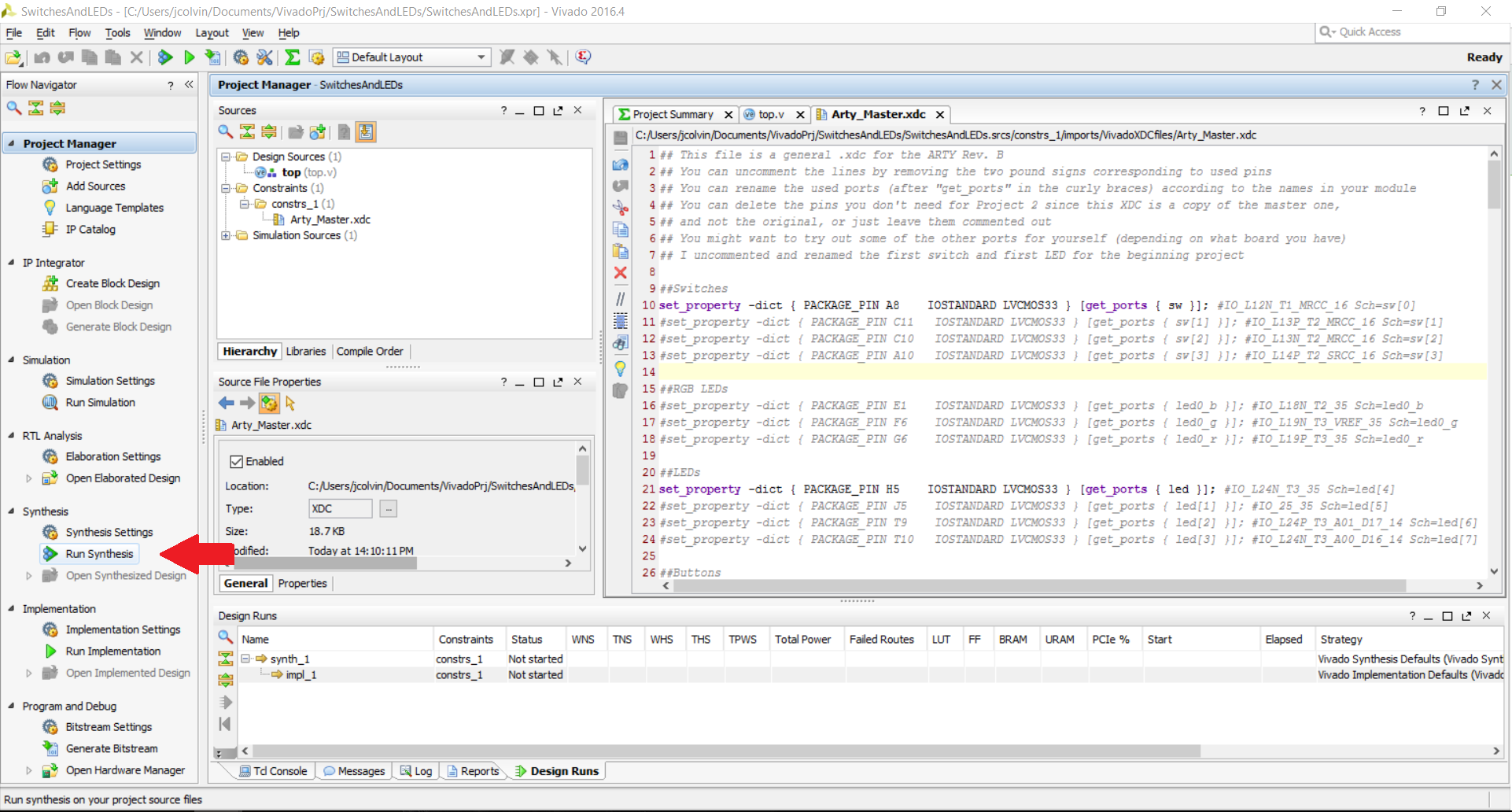

Let’s go ahead and generate the bitstream! In practice you would be able to simply click on the “Generate Bitstream” button on the left hand side of the GUI under the “Program and Debug” subsection but we’ll manually walk through each of the required preceding steps. Presuming your Verilog module and XDC file are already edited to your taste and are saved, go ahead and click on the “Run Synthesis” under the “Synthesis” subsection on the left hand side of the GUI.

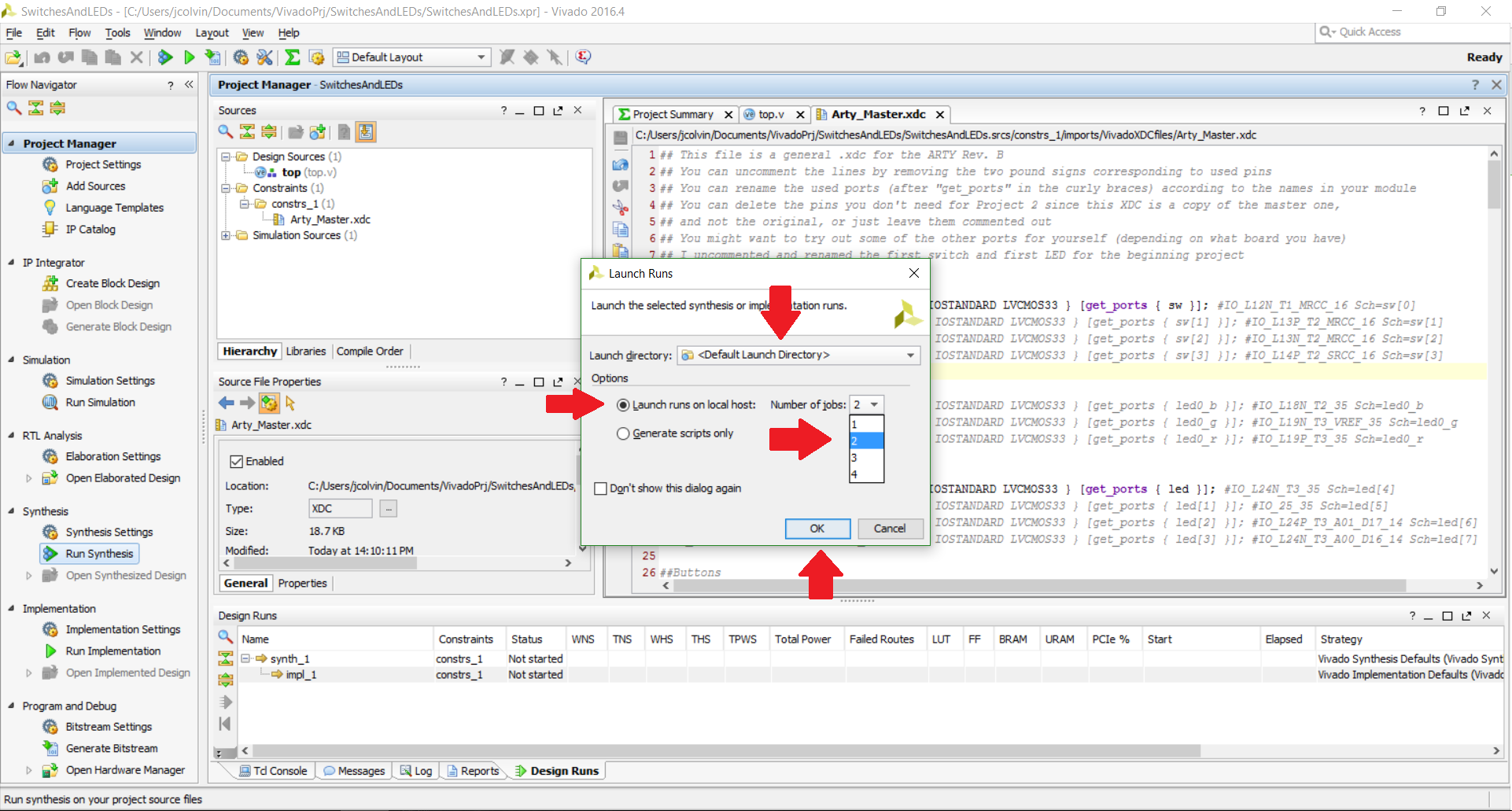

The first time running synthesis (and later times as well if you don’t check the “Don’t show this dialog again” box) you’ll be presented with a wizard showing you some synthesis options. What we want to do leave our “Launch directory” in the “Default Launch Directory” folder and to choose to have the launch run on the local host (your computer) rather than only generating the scripts. You’ll also be given a dropdown option to choose the “Number of jobs” that Vivado can use; this is essentially the number of computer cores that Vivado is allowed to use on your computer. I recommend choosing the maximum number that is available to you as getting a bitstream ready to program an FPGA is very computer intensive. As a side note, the whole combination of synthesis, implementation, and the generation of the bitstream can take quite a bit of time (more than 10 minutes in some cases) since Vivado processes a ton of things hidden to the user and works with the entire FPGA and not just what we are physically utilizing. Click OK after you’re happy with your selections and wait for the synthesis process to complete, which may take a couple of minutes depending on your computer.

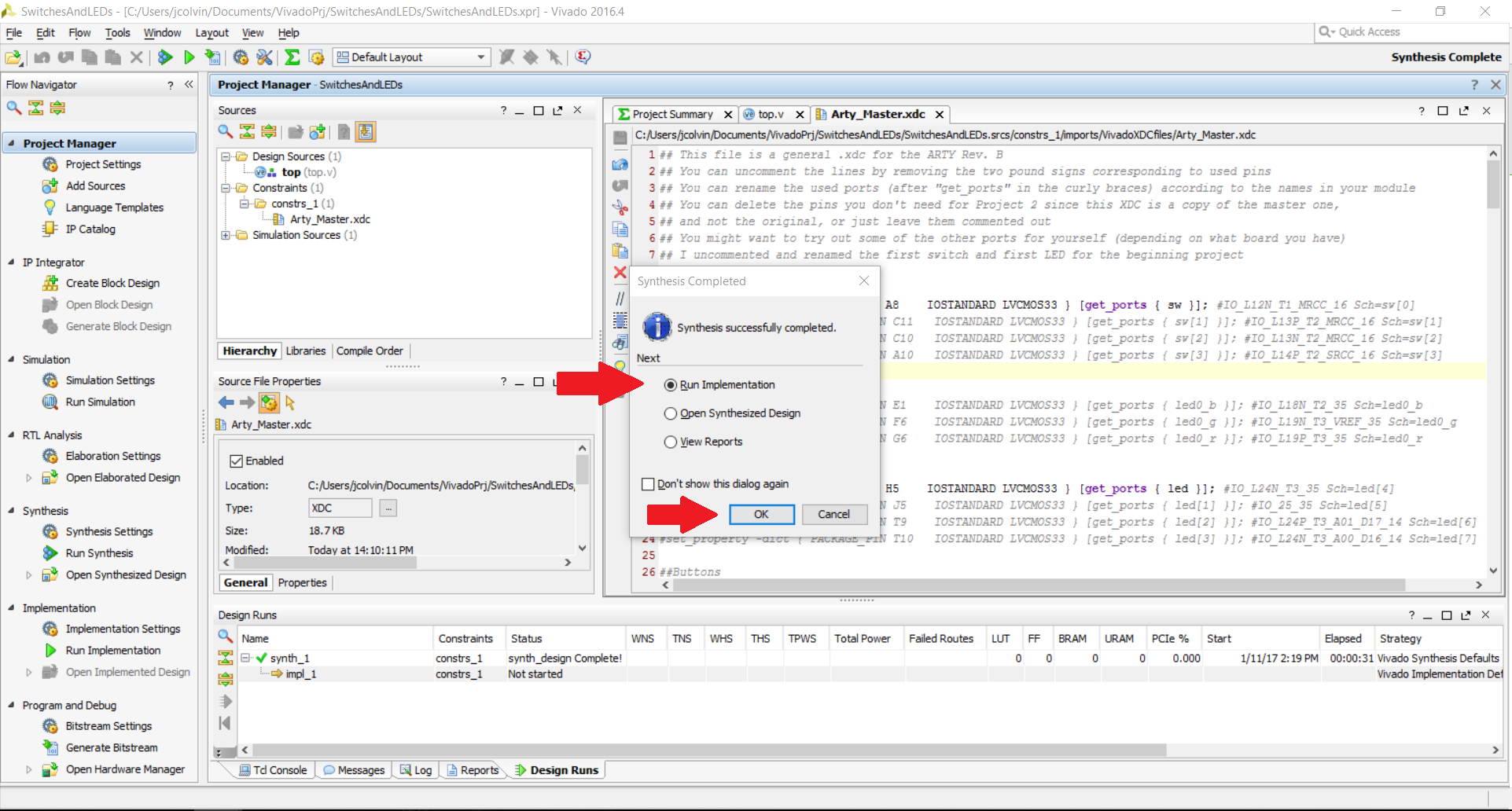

Once it’s done, you’ll then be presented with a popup asking you what you would like to do next. Go ahead and choose the “Run Implementation” option. You’ll then see a similar wizard for the implementation process, where you’ll want to keep the default options, but have the maximum number of cores (jobs) be used. This process also can take a couple of minutes.

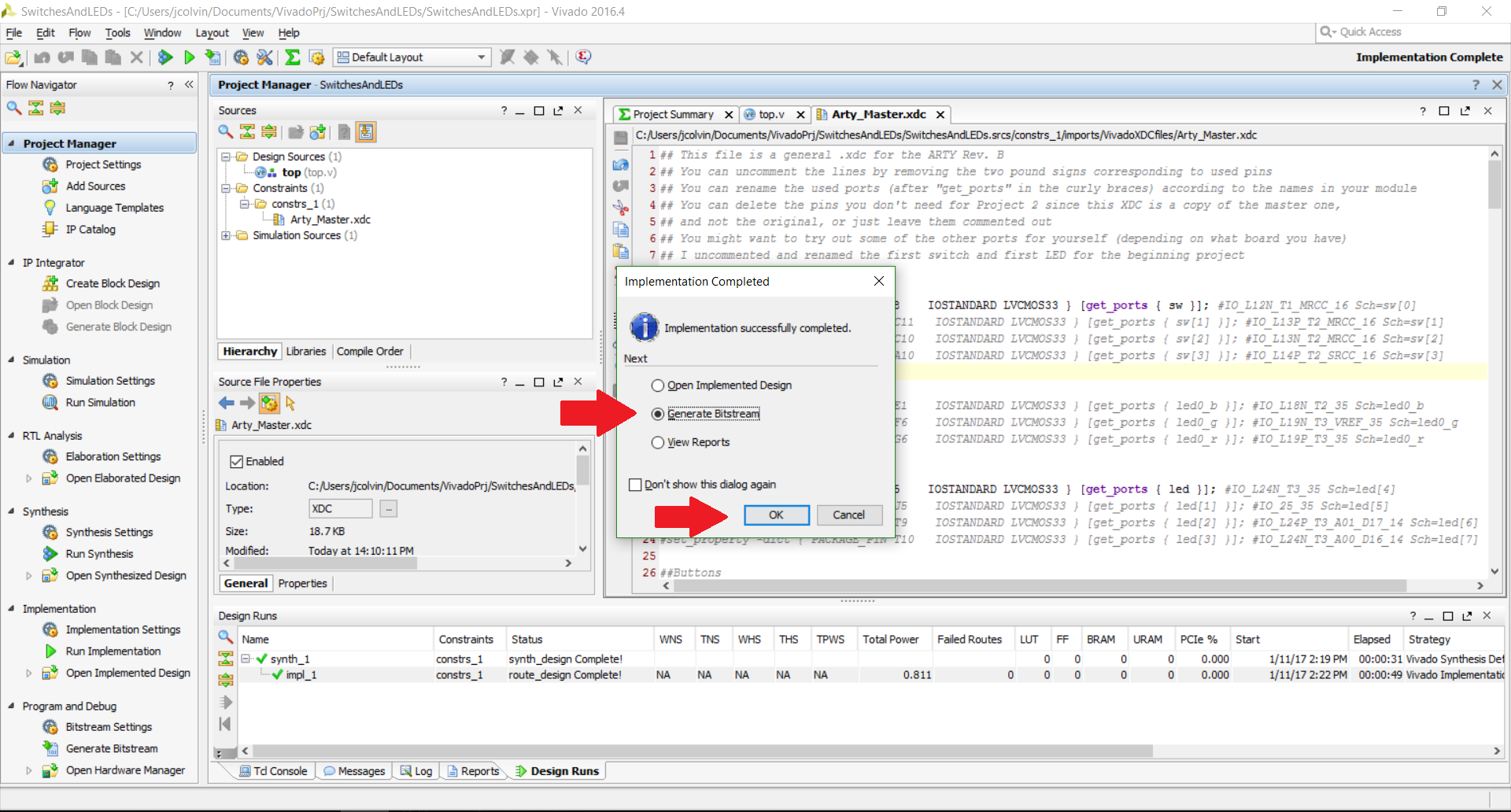

You’ll receive a second popup asking what you want to do next. You’ll want to choose “Generate Bitstream”, but as a side note you may not necessarily want to click on the “don’t show this dialog again” box this time because if you are designing a circuit for your FPGA to run, you may just want to check to see if Vivado was able to successfully make it through synthesis and implementation. If there is an error, you would not want to generate a faulty bitstream. You’ll then be able to choose some bitstream generation options, much like for synthesis and implementation. When you are happy with your selections, click OK to have Vivado generate the bitstream.

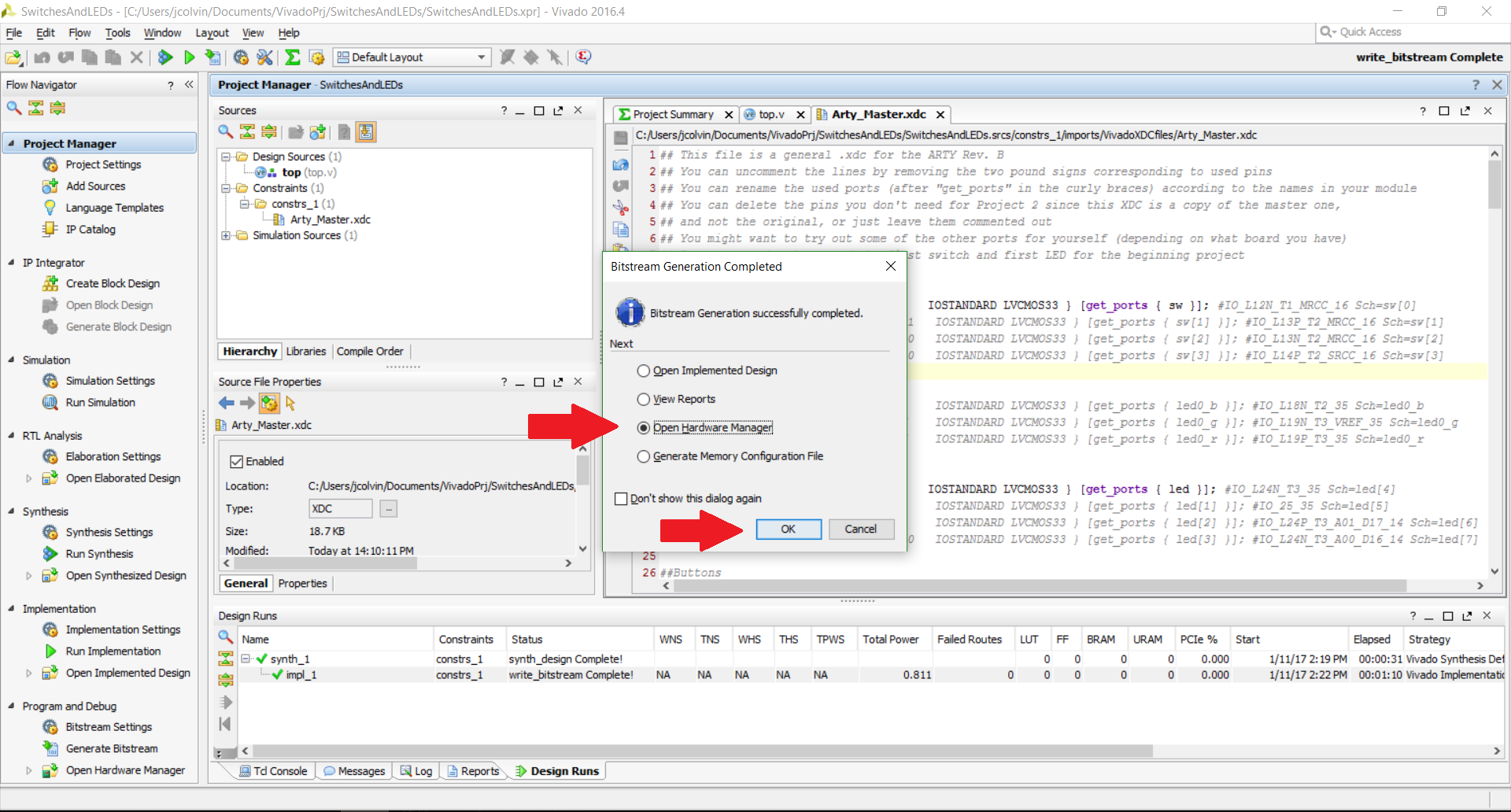

After another few minutes the bitstream will finally be generated and all we have left to do is program our FPGA with it! You’ll see another helpful popup where we will get the option to choose to open the Hardware Manager, which is where we will be able to make sure Vivado is connected to our FPGA.

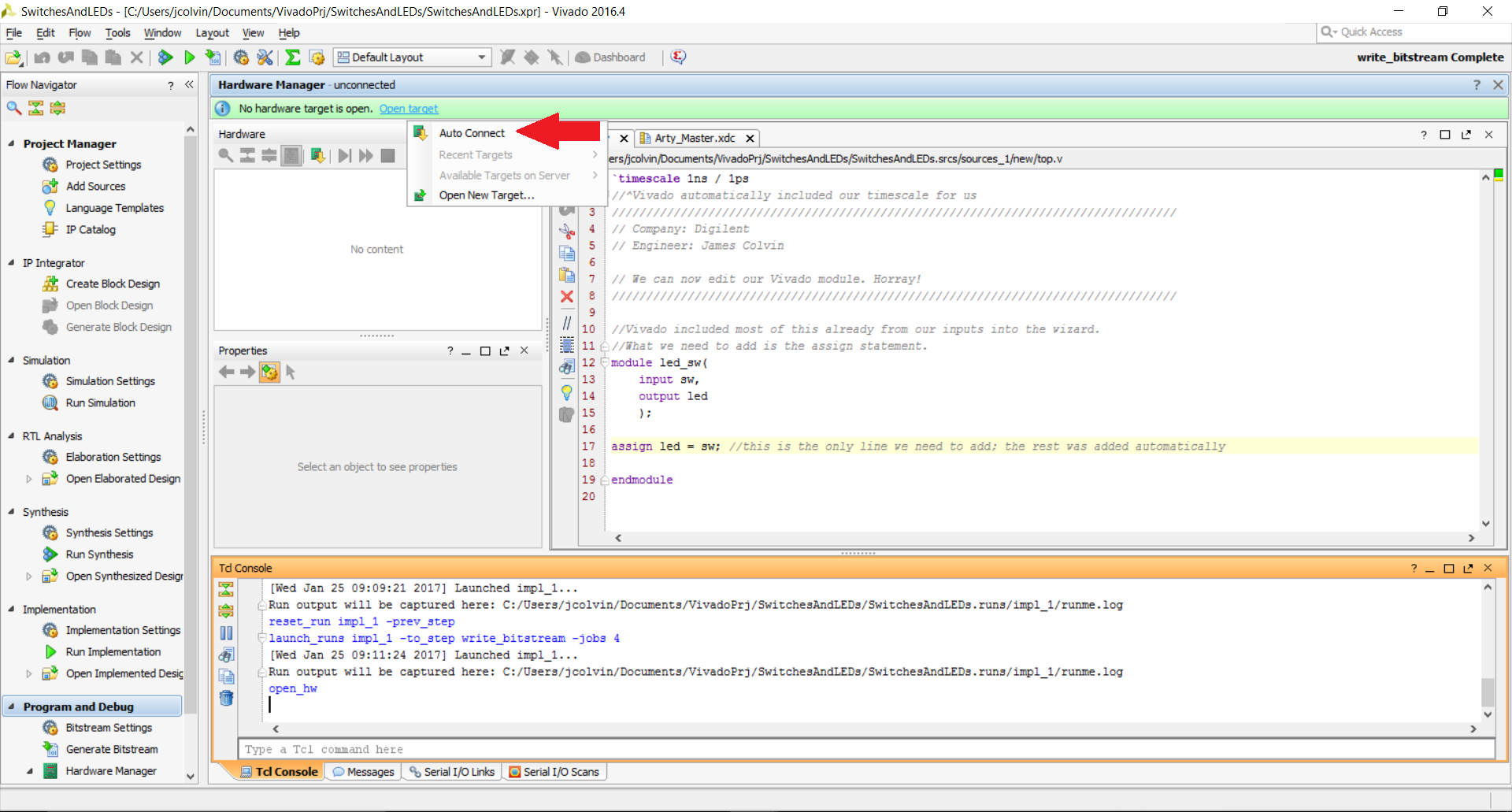

If your FPGA is not connected to your computer already (or if it’s connecting for the first time) you’ll see a green bar at the top that indicates that no hardware target (FPGA) is currently open. After you connect your FPGA to your computer, typically via a micro USB cable, and confirm that the LED power indicator lights turn on, go ahead and click on the “Open Target” button in the green bar and then choose “Auto Connect”.

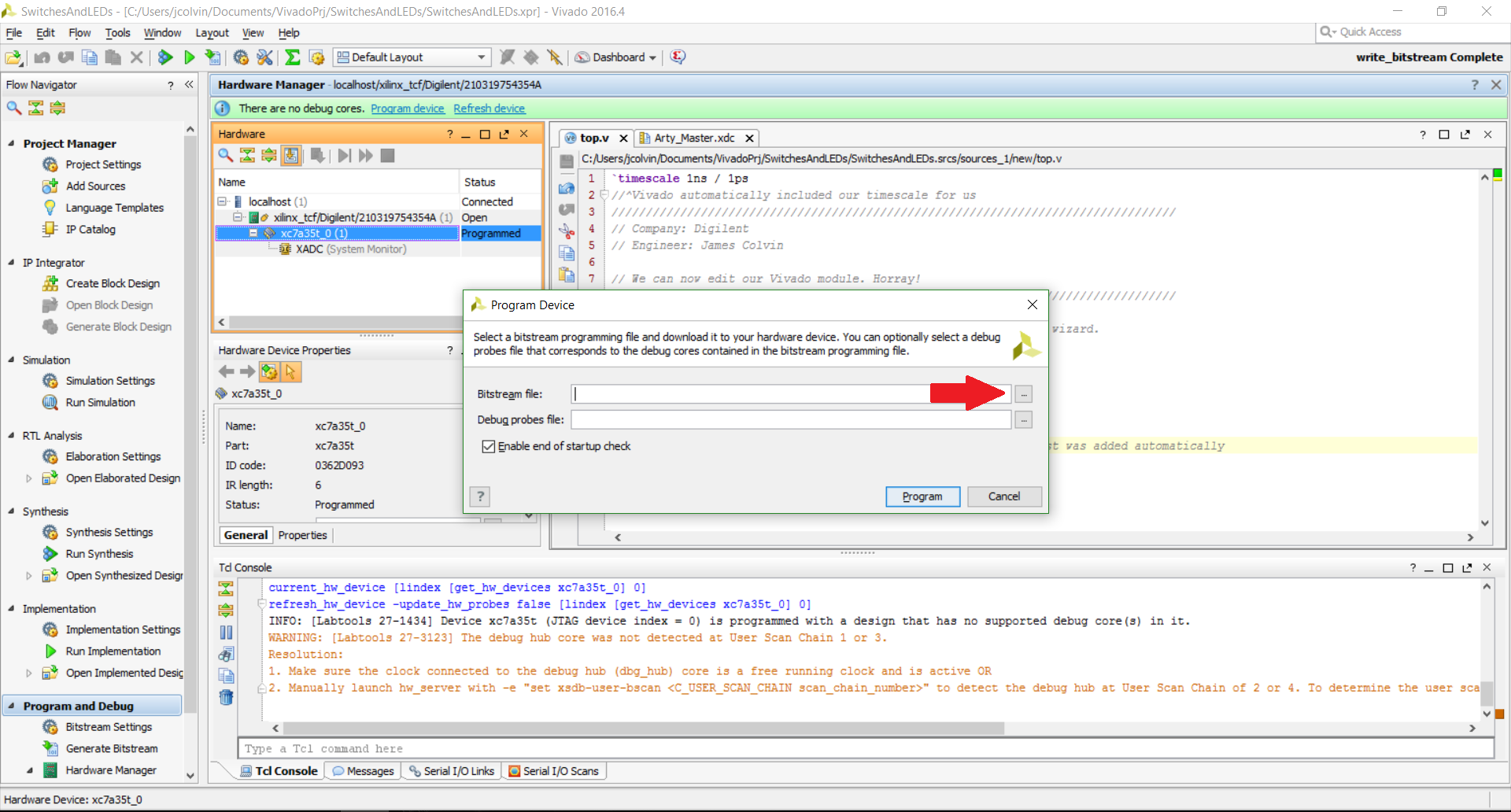

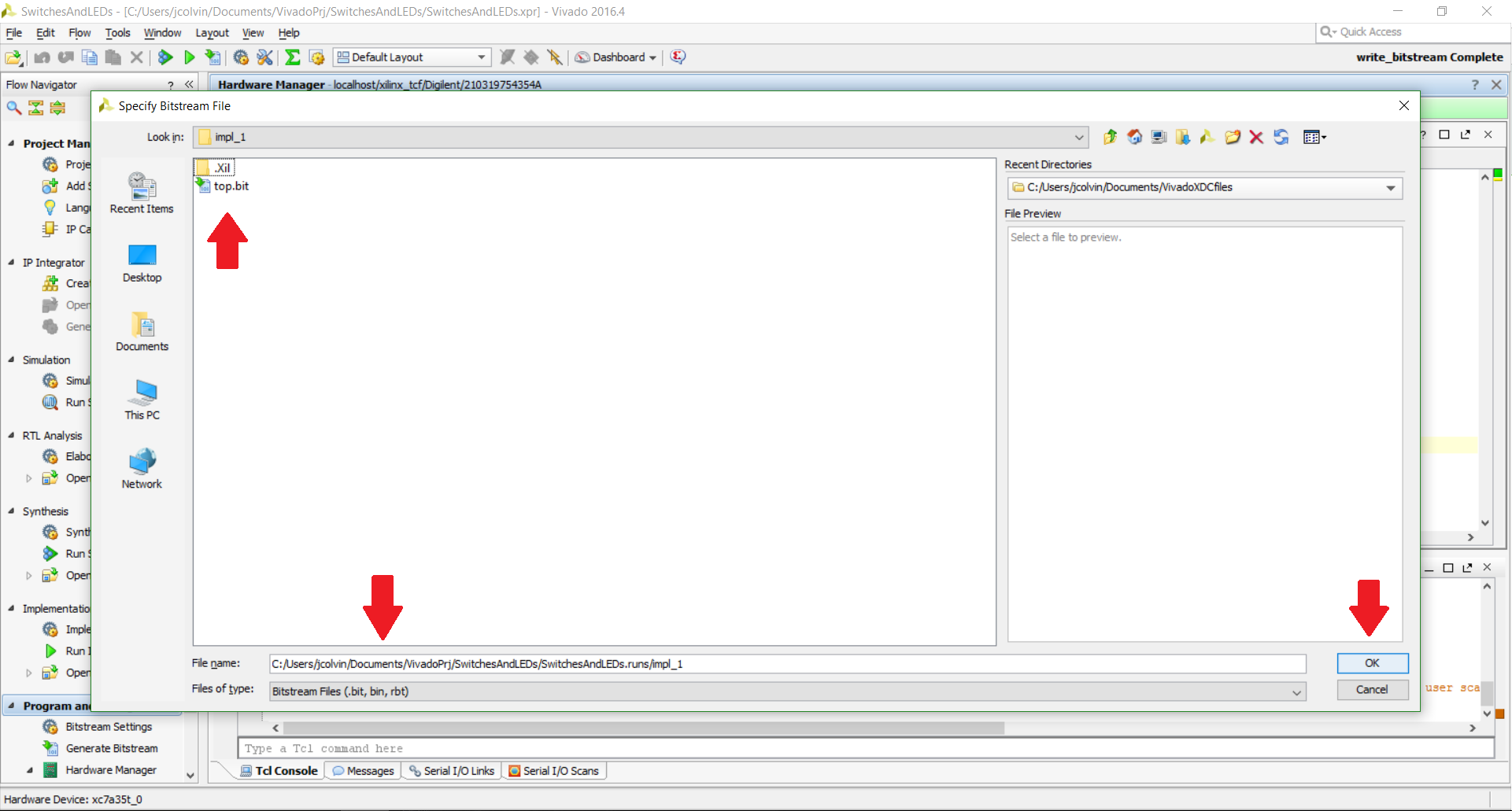

We’ll then be asked to choose the bitstream file to load the FPGA with (we don’t have to worry about the debug probes since we don’t have any in this project). The bitstream file is a little non-intuitive to find; you can locate it by going to the folder where you told Vivado to initially save your project, the yourProjectName.runs folder, the impl_1 folder, and then choose the .bit file that you see. In this tutorial, the verilog module is named top, so the bitstream is called top.bit. Click OK to confirm your selection of the bitstream and then click “Program” (you can leave the “Enable end of startup check” either enabled or disabled). Luckily, the programming process itself will take under 10 seconds, so that’s a nice change of pace.

And we’re finally done! The way I set up this tutorial (and my XDC file) I have the first switch (SW0 on the silkscreen) on the Arty controlling the state of the first monocolored LED (LD4), as evidenced in the picture below.

I hope you all enjoyed this tutorial series!

Please feel free to comment with any questions you have or any other tutorials you would like to see in the future!

can I ask you about bit file? how u can create the bit file? I just started about matlab. thanks

Hello,

Xilinx’s Vivado Design Suite is what creates the bit file. None of us here at Digilent have really worked with MATLAB so we don’t have a ton of advice available for you in that regard. MATLAB does have a nice introduction page that includes some videos on this available on their website here here.

If you have any further questions about this, please post your question on our technical forum, https://forum.blog.digilentinc.com/, where one of the Digilent engineers will be able to see and respond to your question.

Thanks,

James Colvin

Can you suggest any way to run Matlab code in vivado

Vivado itself doesn’t run MatLab code, but we have another post that maybe be of interest to you HERE. This page on MathWorks’ website might be a good one for you as well.

Hi do you think you can create a bitstream for the ravencoin kawpow miner/algorithm?