You may have heard about VAXEL ZERO, the FPGA configuration/operation automation solution that runs on Windows PCs. VAXEL ZERO was developed by a group of seasoned RTL design verification engineers who wanted to take advantage of FPGA to speed up the simulation and test processes but did not want to be bothered by those cumbersome configurations and operations tasks FPGA usually entails.

The single biggest value of VAXEL ZERO is its productivity optimization. It allows you to minimize the time you spend setting up, configuring, and operating our Zynq boards like the Zybo Z7 and Eclypse Z7. Thus, it maximizes the time you can devote to the actual design verification and testing of your logic.

Below are the six main features of VAXEL ZERO.

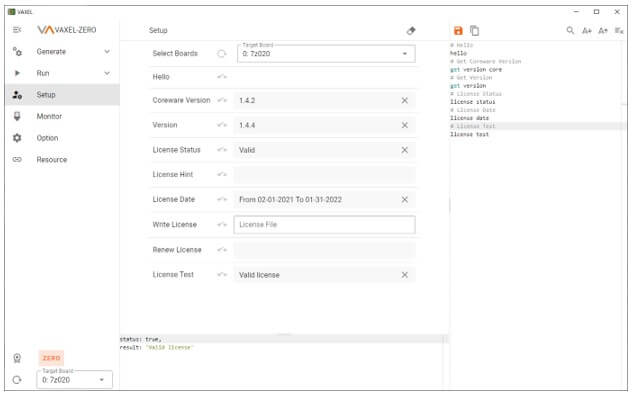

- Effortless setup of Zynq board with VAXEL ZERO (Windows PC): After downloading and installing the VAXEL ZERO package on your Windows PC, setting up VAXEL ZERO on your Zynq board takes zero effort. Everything is visible on the Setup screen as soon as you connect the Zynq board to your Windows PC with a standard USB cable and switch on the Zynq board.

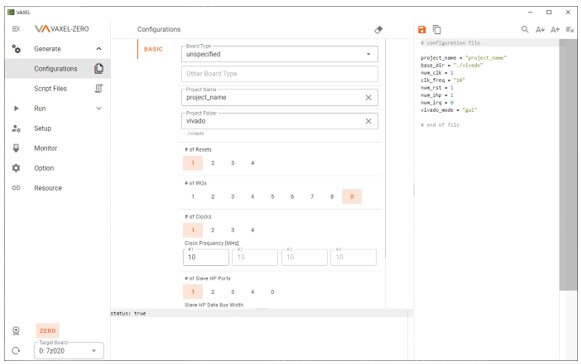

- Easy preparation and configuration of Zynq processors such as clocks and buses: While all engineers desire to focus on verification and testing of their RTL designs, using FPGA usually means they must allocate a frustrating amount of time to preparing and configuring the processors on board FPGA, such as the clocks and buses. As shown below, VAXEL ZERO provides a tool that allows you to be done with the Zynq processor configuration just by filling out a few parameters with GUI.

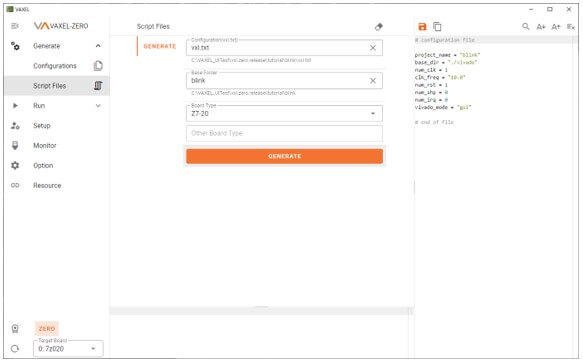

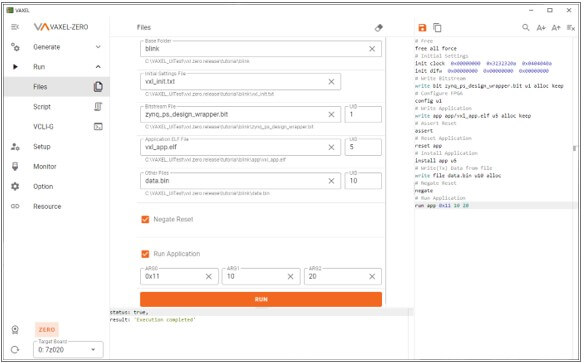

- Easy generation of PS and sending the bitstream to Programmable Logic: Once the Zynq processor configuration has been completed, you are ready to generate the Zynq processor system (PS) portion with the VAXEL ZERO UI. When the PS portion is ready, you can package it with your bitstream for the programmable logic (PL) and transmit it to the Zynq board as shown in the screenshot below.

- Your logic control program and application program (C code) will be automatically uploaded to one of the ARM processors: Besides uploading the C application program onto one of the ARM processors on the Zynq board, VAXEL ZERO comes with a nice GUI that allows you to operate the application from a Windows PC but just sending the parameters.

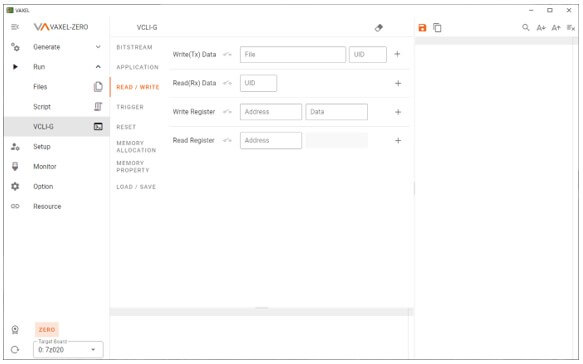

- VCLI gives you a command line capability for managing resources internal to FPGA. Initial debugging is extremely productive: VCLI is a proprietary command line interface. It comes with a set of easy and intuitive commands for managing the FPGA resources.

- VAXEL ZERO’s existing Python library allows you to build and run some complex test scenarios that are written in Python: Today, Python is one of the most widely used programming languages globally. We decided to equip VAXEL ZERO with a Python library that allows any Python programs to be executed on FPGA from a Windows PC.

————— Sample code in Python —————

def test_one( test ):

print( ‘—- Test #{0} —-‘.format( test[0] ) )

# Clear resources

clear()

# Get PL base address

pladdr = vxl.get_pladdr()

# Transfer test data

write_file_to_uid( UID_INPUT_IMG, test[3], 0 )

if len( test[4] ) > 0 :

write_file_to_uid( UID_LUT_R, test[4], pladdr+REG_IMGFLT_LUT_R )

if len( test[5] ) > 0 :

write_file_to_uid( UID_LUT_G, test[5], pladdr+REG_IMGFLT_LUT_G )

if len( test[6] ) > 0 :

write_file_to_uid( UID_LUT_B, test[6], pladdr+REG_IMGFLT_LUT_B )

# Run application

print( ‘Run application’ )

vxl.run_app( test[1], test[2], 0 )

# Send trigger to finish application

vxl.set_trig( TRIG_EXIT_APP, 1 ) # set trigger in advance

# Wait for finish signal

while( vxl.stat_app()[0] & vxl.VXL_STAT_EXIT ) == 0 :

pass

print( ‘Finish application’ )

Click here for a FREE 12-week trial (regular price $499/year) through VAXEL’s site