Recently, I have been working on a project using the Arty and MicroBlaze. The Arty has four headers for use with the Digilent Pmod line-up. As I don’t have much experience with the AXI4 protocol that MicroBlaze uses for peripherals, I looked for a quick way to interface with these headers.

Luckily, Vivado has the ability to use pre-compiled code. These pieces of code are called IP cores. IP stands for Intellectual Property, and most have a license associated with them. The functionality of the cores range from interface protocols to data processing blocks. Some examples include the Clocking Wizard, for generating a clock without a clock divider, and MicroBlaze, a soft core processor.

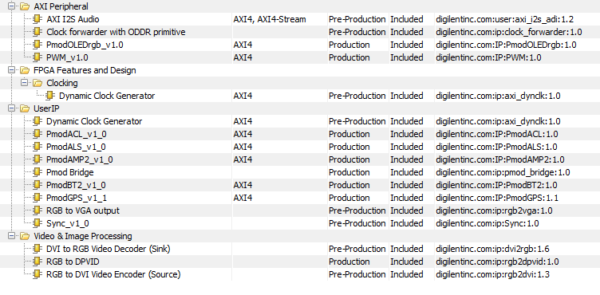

Digilent maintains a repository of free-to-use IP for Vivado that is helpful when working with a MicroBlaze design.

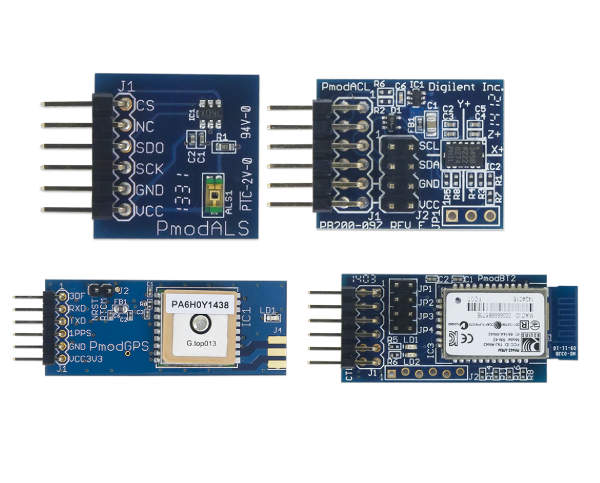

Included in the Digilent IP cores are Pmod specific cores, as well as some video conversion blocks. Some examples are the PmodALS, PmodACL, PmodBT2, and PmodGPS. These all have blocks available in the repository.

The IP cores work for our FPGAs and can be programmed with Vivado. These include the Arty, Basys 3, and Nexys 4 DDR boards.

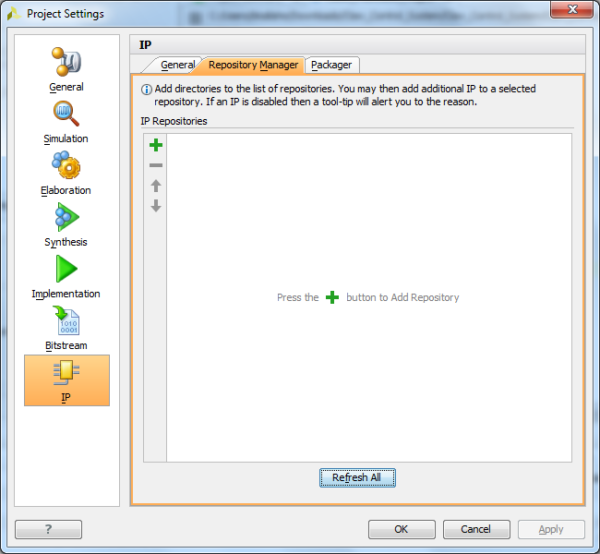

For detailed instructions for adding the Digilent IP cores, follow my tutorial on Instructables.com which goes through adding cores for all new Vivado projects as well as for older projects, step by step. The Instructable goes through adding IP to a single project as well as for all future projects generated by Vivado. It is all done with the power of the Vivado IP Repository Manager.

For more information about our FPGAs and Pmods, visit the store.