For years, hardware engineers with interchangeable I/O needs had two strong choices – our own Pmod, which was developed as an open standard back in 2004, as well as the FPGA Mezzanine Card (FMC), developed by a consortium of companies and end users and fronted by Xilinx. Both Pmods and FMC had their own specific uses – but what if you needed something else when designing an FPGA?

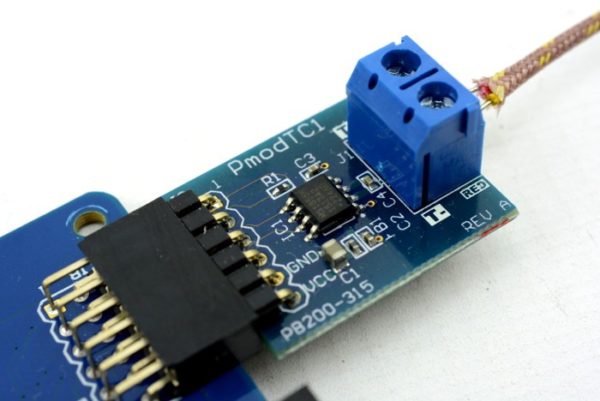

Pmod

The Pmod standard uses a 6-, 8-, or 12-pin communication protocol with LVCMOS 3.3 V logic conventions. It was initially designed for use in Academia, but quickly found a home in professional designs as well. It did a good job of removing the cost barrier, as Pmod devices are typically very efficient and cost-effective. In taking advantage of popular serial protocols (SPI, I2C, and UART), it was recognized as a flexible option for rapid prototyping. They also allow for more effective designs by routing analog signals and power supplies only where they are needed, and away from digital controller boards.

However, there are some limitations.

Though affordable and flexible, the low pin count can make Pmod unsuitable for some peripherals with heavier resource demands or applications that require higher frequency outputs. There is also a lack of impedance control on most devices.

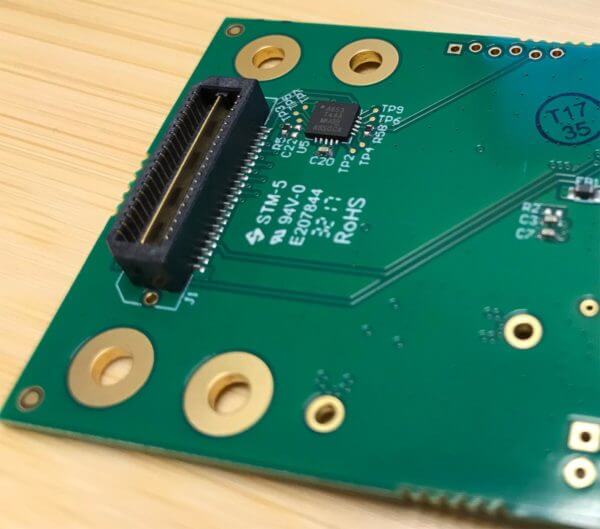

FMC

On the other end of the FPGA I/O spectrum, the FMC standard provides much higher range of acceptable signaling speeds (up to 10 Gb/s!). The design simplicity significantly reduces power consumption, IP core costs, engineering time, and latency. The FMC Standard also promotes the ability retarget existing FPGA card designs to a new I/O.

However – there’s always a drawback, isn’t there? – with a single-width (69 mm x 76.5 mm) or Double width (139 mm x 76.5 mm) form factor, the FMC does require quite a bit more real estate on an FPGA board. Improved signaling speeds also mean that it has a higher FPGA pin consumption. In addition, with all of these features, the FMC Standard is – you guessed it – more expensive.

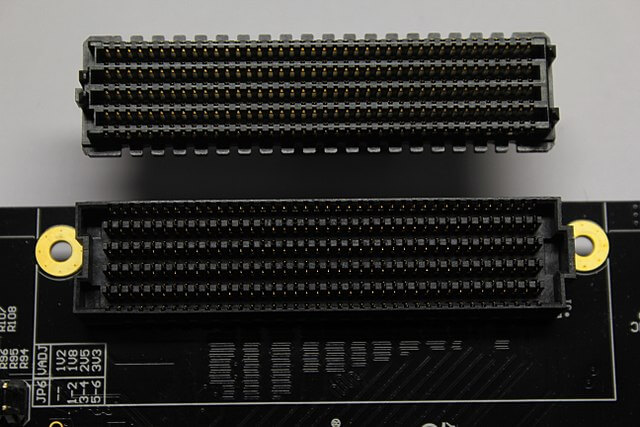

SYZYGY

Noting that a majority of FPGA enthusiasts and designers were using one of the aforementioned standards, Portland’s Opal Kelly went to work on an FPGA standard that straddled the differences between Pmod and FMC but create a happy medium that also exploited the benefits of each. In 2017, SYZYGY (sih-zuh-gee) was unveiled. Each limitation and strength that was brought up earlier seems to have been addressed with the new standard: moderate pin count, high performance speeds, medium cost barrier, voltage flexibility with SmartVIO, better pin utilization with standard/transceiver cross-compatibility.

The advent of SYZGY is important for a couple of reasons: it gives Pmod users the ability to expand their capabilities without the limitations of Pmod and FMC users a way to ditch the resource-prohibitive specs of FMC.

The SYZYGY standard is open source, and we urge intrepid designers to see what they can do with it. We’ve used it on a couple of our newest boards (the Eclypse Z7 and Genesys ZU) and converter modules (Zmod ADC and Zmod DAC) to very positive reviews.

Any plans to use Qwiic connectors in your future products?