Implementation of an instruction pipeline is a common technique used when working with microprocessors. Pipelining improves operation and processing time. Microprocessors such as the Microchip® PIC32MX460F512L on the chipKIT Pro MX4 board use this technology to provide efficient processing and instruction execution. Though the process is sophisticated, it is actually quite simple in concept. In my explanation of instruction pipelines, I’ll specifically refer to the Microchip PIC32 microprocessor that I mentioned above.

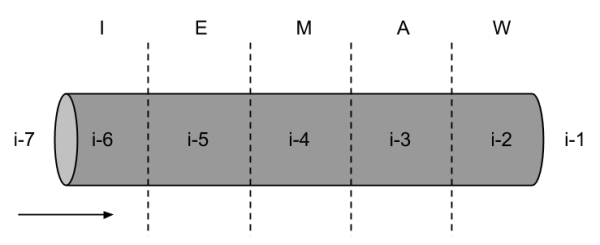

The PIC32 executes instructions with a 5-stage pipeline. These 5 stages are as follows:

- Instruction stage (I)

- Execution stage (E)

- Memory stage (M)

- Align stage (A)

- Write back stage (W)

An instruction is fetched in the instruction stage and decoded in the execution stage. Operations are then completed in the memory stage, resulting data is aligned in the align stage, and data is written back to what’s called the register file in the write back stage. Thus, an instruction goes through 5 separate stages before all relevant operations are completed. That being said, every instruction would take 5 clock cycles to complete, assuming one clock cycle per stage. 5 clock cycles might not seem like much, especially at the PIC32’s operating frequency of up to 80MHz, but computing is all about efficiency! That is where an instruction pipeline comes in. Rather than sending one instruction at a time and waiting for all 5 stages to complete before the next instruction, a pipeline allows five different instructions to be operated on simultaneously.

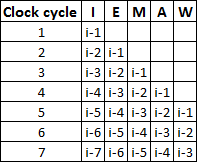

Say we have instructions i-1, i-2, i-3, and so on, and refer to the diagram above. Instruction i-1 is fetched first. After one clock cycle i-1 continues to the next stage of the pipeline. As soon as i-1 is in the execution stage, the computer can fetch the next instruction, i-2. With another clock cycle, i-1 is decoded and continues to the memory stage. Instruction i-2 has been fetched and continues to the execution stage, and the computer can fetch yet another instruction, i-3. You’re probably starting to get the drift by now. Essentially, 5 instructions are managed at once, one in each stage of the pipeline. You can see from the diagram that once the pipeline is full, an instruction is completed with each single clock cycle. It is clear how this is substantially more efficient than completing one instruction every five clock cycles.

Lastly, to make the concept a little more clear, you can think of an instruction pipeline as, well, a pipeline. All five stages, or sections, are filled with five different instructions and one instruction is completed with each clock cycle. Check out the picture below.