Recently I was converting some HDL from the Basys 3 to the Arty and ran into what seemed to be an unsolvable problem. After some testing, I found that the reset button that was used was Active High in the code I was converting. Once I knew this, the rest of the conversion went smoothly.

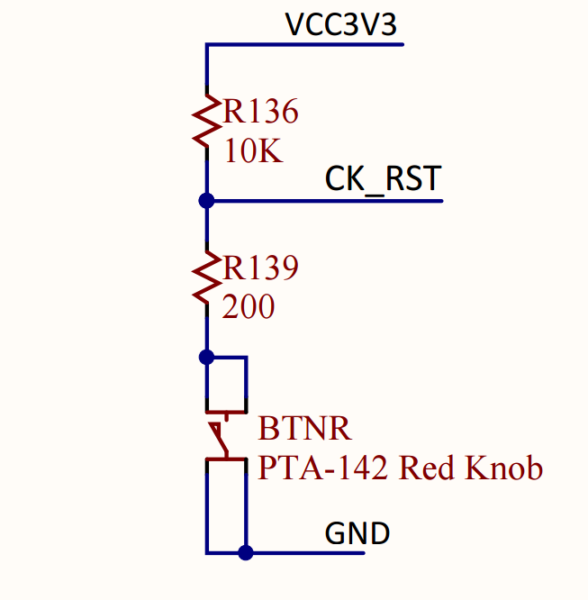

To avoid this hassle there are two ways to find out the polarity of a button. The first is to look at the schematic for the board. The are two configurations that this could have, Active Low and Active High. For Active Low the circuit looks like:

The important thing to see in this image is that one side of the button is connected directly to ground (GND). For Active High the circuit is a little different:

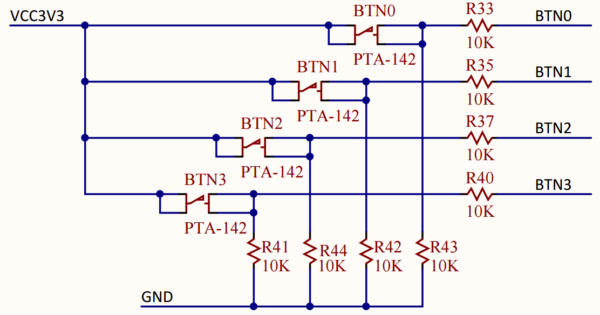

This image shows the four user buttons on the Arty. Notice that these are directly connected to the 3.3 volt power line (VCC3V3). Both of these images were pulled directly from the Arty schematic.

The second method is to write a test project that takes the button as an input and uses a general purpose pin as an output. In Verilog this would look something like this:

module btn_test (input btn, output gpio);

assign gpio = btn;

endmodule;

After generating the output, a multi-meter can be used on the output pin and the button can be pressed to find the polarity of the button.

Also important to note is that on some of our boards the 7-segment displays are Active Low. A good way to test this is to use the button that was just tested to trigger one of the segments. This would look like the following in Verilog:

module btn_test (input btn, output an, output [6:0] cat);

assign an = 1’b1;

assign cat = 7{btn};

endmodule;

This small module will take the button as an input and drive all 7 cathodes based on the state of the button. One of the digits should show an eight.

Now that you can find out the polarity of your I/O you can go forth with converting your projects from one board to another. Have you ever experienced issues with signal polarity in the past? What other problems have you run into when working with FPGAs?