Our very own Alex, known on Instructables as alexwonglik, did this project written written in Verilog to create a 3-bit binary counter. This project was initially done for an online class. The clock divider and counter modules were provided in the class Alex worked on this for.

This project requires a Basys 3 and the Vivado Webpack. It was originally done with the Basys 2 and Xilinx ISE, but was updated by the Instructables author.

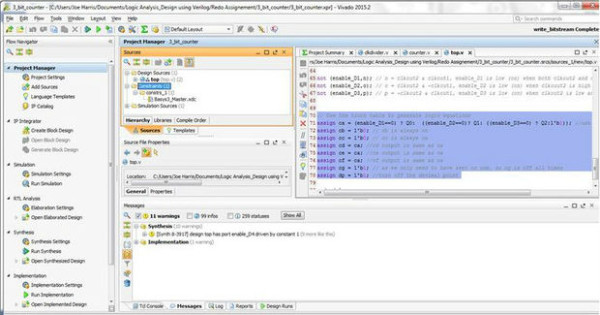

To write the top module to display 3-bit output from the counter on the board’s 7-segment display, Alex began by installing the Vivado Webpack from Xilinx. After doing that, you should create a project. Then, create the clock divider and counter module. You’ll then create the top module and modify the constraints file. At that point, synthesize and implement the design. Generate the bitstream, target the hardware, and then program the device. Presto!

This is a neat project and a great way to learn more about using the Basys 3 and Vivado. Comment on Instructables to let Alex know your thoughts and here to tell us about any ways you’ve used the Basys 3 lately.

One Comment on “Making a 3-Bit Binary Counter with the Basys 3”