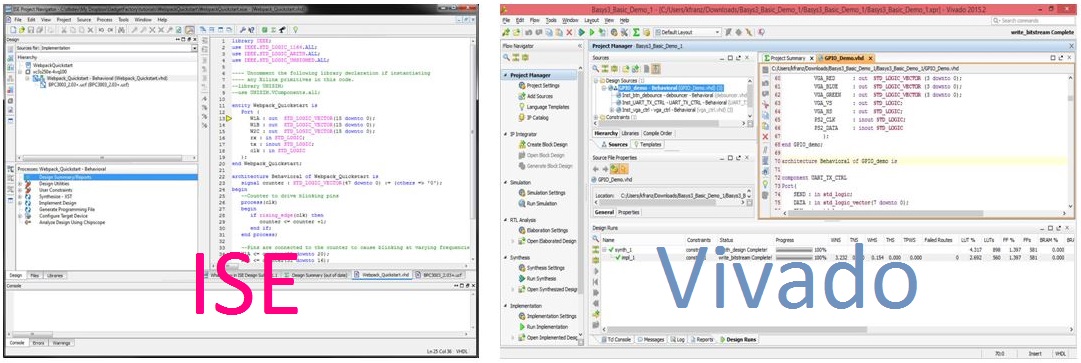

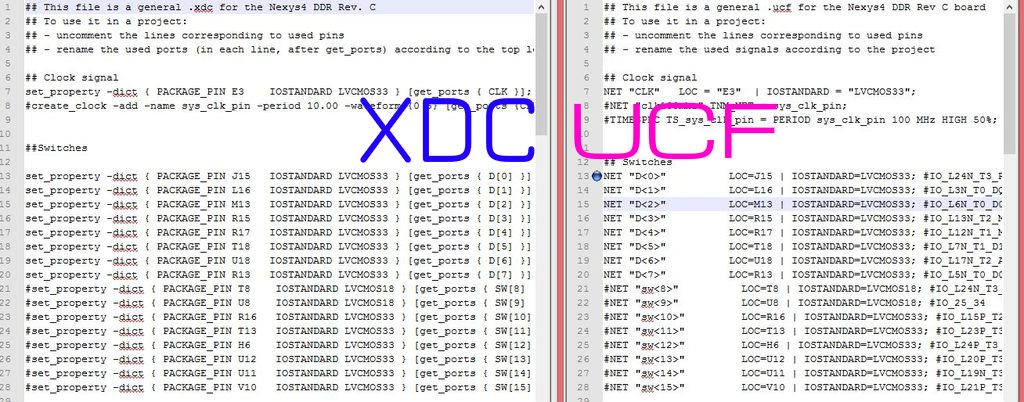

A little while ago, I wrote a post introducing everyone to the constraints file. The file that maps nets to physical pins in an FPGA design. If you missed that post, you can check it out here. Part of the reason I wrote that post was because of the increasing number of Forum questions regarding constraints files, and converting projects from Xilinx ISE to Xilinx Vivado.

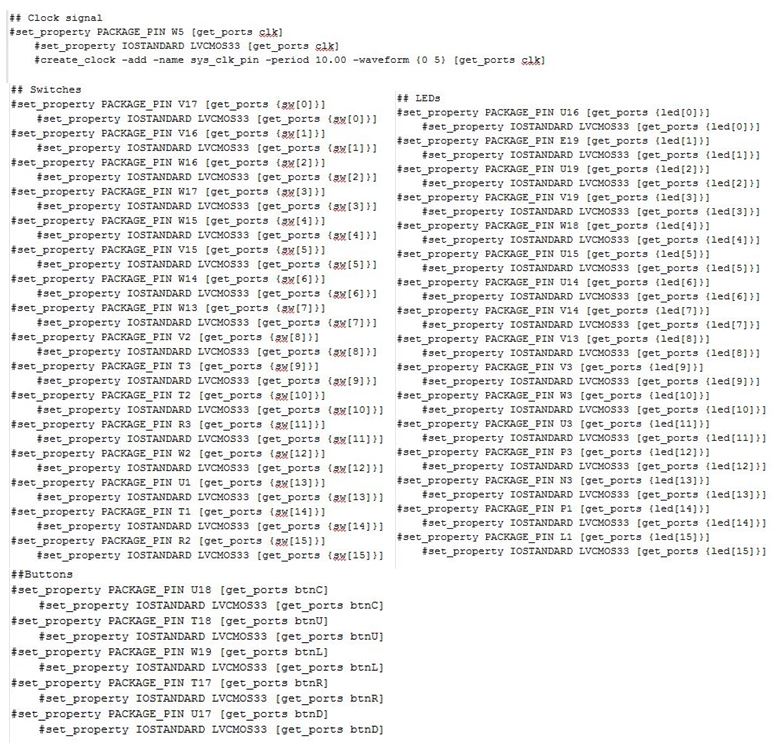

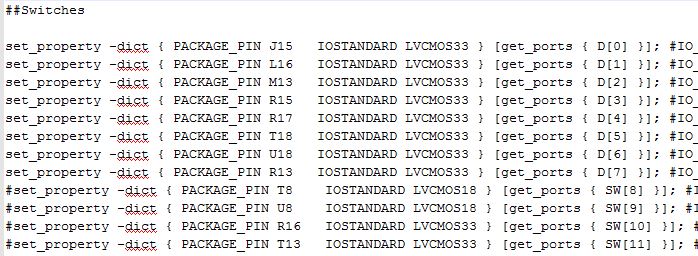

If the project contains no IPs, then all you have to do is convert the UCF file into a XDC file. However, if you don’t understand what the file is for or have never worked with one, it can be a little confusing. So I wrote the post introducing the constraints file, UCF and XDC being constraint files.

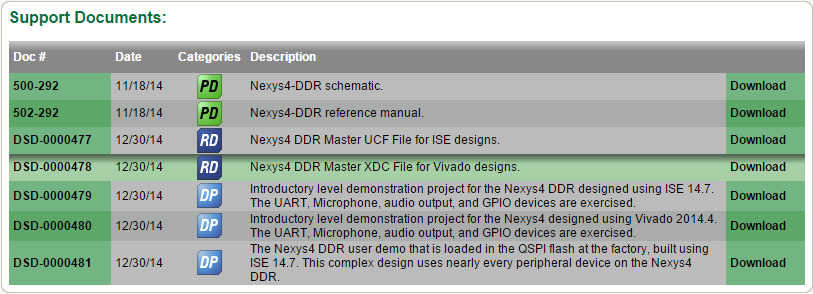

However, I discovered that it might be useful to write a guide on how to convert from UCF to XDC file. There are a few reasons that you may have to do this. For example, if you upgrade your board from an ISE-compatible board to one that’s only compatible with Vivado, like the changing from Nexys 3 to Basys 3, or Basys 2 to Basys 3. Alternatively, you could be upgrading software by choice, like with the Nexys 4 DDR, which is compatible with both ISE and Vivado. And lastly, you could be trying to use an old demo written for a different board than the one you have.

Either way the steps are the same:

- Download the Master XDC for the new board.

2. Find all the nets in use in the old UCF file.

3. Find those same components in the new XDC file.

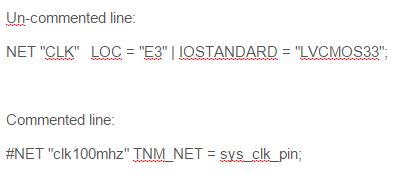

4. Un-comment those nets.

5. Change the net names to match the old file.

To view the full, more detailed instructions you can view the instructable here.

Hi,

Good article, it has been really helping us to map from .ucf to .xdc file.

However, we would like to know more about area constraints and power constraints mapping into .xdc file.

kindly provide quick tutorial and more useful commands of TCL/Tkl language in vivado.

Regards,

Mamidi Nagaraju,

Do you know where I can find a specification for XDC constraints? I just purchased an ARTY board and I wish to use it to develop some of my own designs/IP and tools. Part of the reason for this is that I want to use these to teach my daughter (who just started at U of I) how to do Logic/FPGA design. I want her to understand how to do design, so initially I want her to do the designs without using wizards or use design files created by someone else. When she really understands the details and can do a complete design from scratch, it will then make sense to use tools that automate time consuming tasks that speed up the design process. This is why I would like to have a specification for XDC constraints.

Thanks,

Peter Baran

— My first FPGA design used a Xilinx XC3020