Recently the Ritsumeikan University VLSI Center held an OpenCV image processing workshop with FPGA

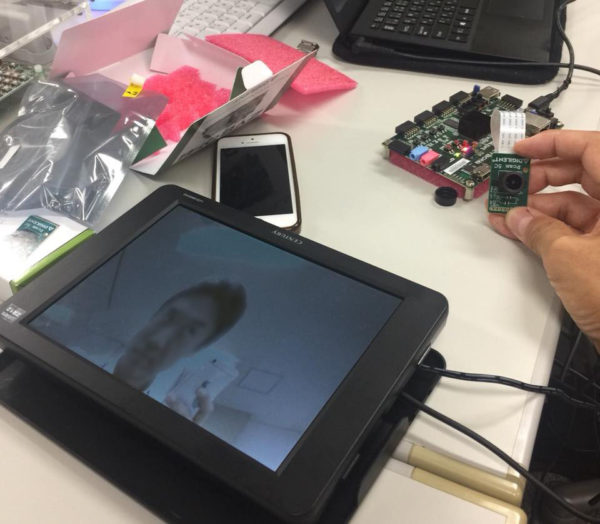

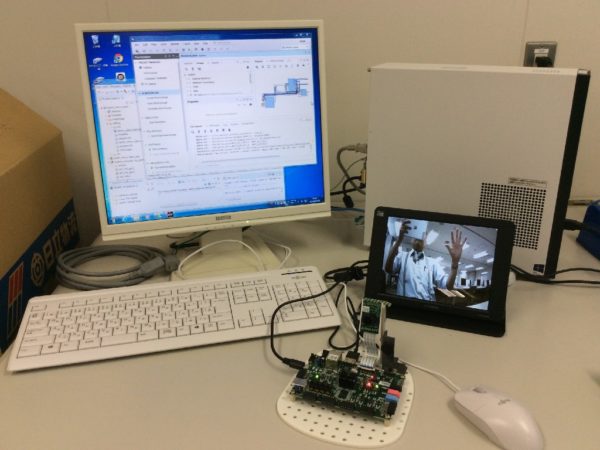

and automatic driving contest exchange meeting. The workshop was primarily aimed at people who wanted to acquire high-level synthesis, image processing, and pipeline design through Xilinx FPGA. The workshop used Digilent Embedded Vision Bundle consisting of Zybo Z7 powered Xilinx Zynq SoC and Pcam 5C 5MP camera sensor.

Professor Izumi, who ran the workshop, was inspired to host this training after attending the Embedded Vision workshop sponsored by Digilent, Avnet and Xilinx. He wanted to help other academia in the area learn about the latest embedded vision.

The workshop went further in depth, teaching attendees how to use OpenCV and Digilent embedded vision bundle to build the embedded vision applications. It was suited for both hardware designers and software developers, with 40 attendees in total.

It is exciting to see professors taking material a step further and widening the audience, and we are looking forward to what people create with embedded vision!

Any chance an archive video or workshop material is available to look at? It would be fun to see if my High School Mechatronics Engineering students could learn from it. I have Pynq, and a few Xybo’s and cameras to play with…