Go Back to the PmodIA Resource Center

PmodIA User Guide

This user guide is (clearly) not completed yet, but I found that the reference manual I was writing was getting way too long explaining how one might measure the impedance of a discreet component/circuit and providing the associated data streams that would be needed.

So, I have instead relocated the text to this user guide for people who are interested in what they might need to do if they did not want to use/cannot use the associated MPIDE library.

Determining the Impedance

Here I outline a process for calculating an unknown impedance value.

Calculating the Gain Factor

Before any useful calculations can occur, users must first calculate the gain factor associated with the PmodIA. To do this, users need first set the AD5933 into standby mode and the PGA gain to 1, choose an output excitation voltage and calibration frequency, and choose a known calibration impedance value such as 200 kΩ to place between the two SMA connectors. The default Master Clock Rate (MCLK) that is used internally by the PmodIA is 16.776 MHz.

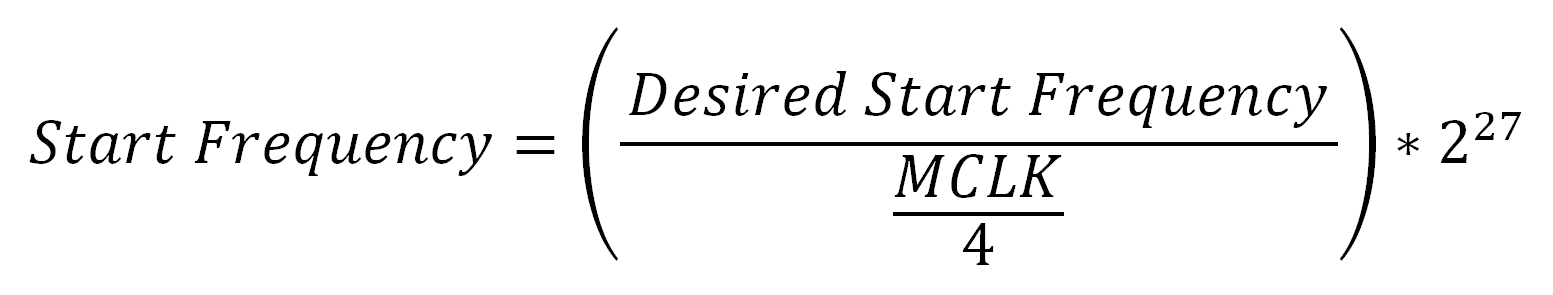

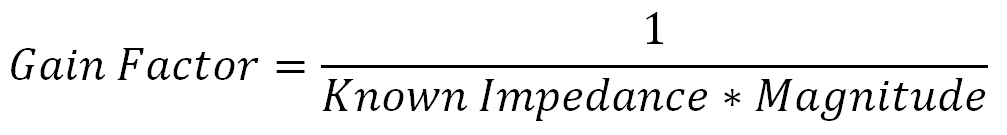

The 24-bit value that represents the desired calibration frequency can be determined from the equation below:

PmodIA Frequency Calculation

The set of registers and their associated bits that need to be written to to accomplish this are provided below:

| Start Condition? | Slave Address and Command | ||||||||

|---|---|---|---|---|---|---|---|---|---|

| Yes | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | (ACK) |

| Start Condition? | Control Register Address | ||||||||

| No | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | (ACK) |

| Start Condition? | Control Register bits | ||||||||

| No | Standby Mode | No Operation | Output Excitation Voltage² | PGA Gain | Response | ||||

| 1 | 0 | 1 | 1 | X¹ | D10 | D9 | 1 | (ACK) | |

| Start Condition? | Slave Address and Command | ||||||||

| Restart | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | (ACK) |

| Start Condition? | Start Frequency Register Address | ||||||||

| No | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | (ACK) |

| Start Condition? | Start Frequency first 8 of 24 bits | ||||||||

| No | D23 | D22 | D21 | D20 | D19 | D18 | D17 | D16 | (ACK) |

| Start Condition? | Start Frequency second 8 of 24 bits | ||||||||

| No | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | (ACK) |

| Start Condition? | Start Frequency last 8 of 24 bits | ||||||||

| No | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | (ACK) |

¹ – Don't Care bit

² – 0 and 0 result in a 2V peak to peak range, 0 and 1 result in a 200 mV peak to peak range, 1 and 0 result in a 400 mV peak to peak range, 1 and 1 result in a 1V peak to peak range

Once the desired frequency is programmed into the PmodIA, users can program the module to Initialize with Start Frequency to allow the frequency generator to reach steady state; the time frame to wait for the frequency generator to reach steady state is entirely decided by the user, as per AD5933 reference manual. Once that time period has passed, users may issue a Start Frequency Sweep command. The internal ADC will sample the measured impedance after a set number of settling time cycles have passed and store the processed result in the Real and Imaginary Data registers.

The set of registers that need to be written to or read to successfully obtain the impedance information, including programming the number of settling time cycles is provided below:

| Start Condition? | Slave Address and Write Command | ||||||||

|---|---|---|---|---|---|---|---|---|---|

| Yes | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | (ACK) |

| Start Condition? | Pointer Command | ||||||||

| No | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | (ACK) |

| Start Condition? | Settling Time Cycle Register Address | ||||||||

| No | 1 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | (ACK) |

| Start Condition? | block write command | ||||||||

| No | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | (ACK) |

| Start Condition? | Desired number of bytes is 2 | ||||||||

| No | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | (ACK) |

| Start Condition? | Byte 1 of 2 of Block Write | ||||||||

| No | Don't Care | 2-bit Decode | MSB of settling cycles | Respond | |||||

| X | X | X | X | X | D10 | D9 | D8 | (ACK) | |

| Start Condition? | Byte 2 of 2 of Block Write | ||||||||

| No | Number of settling time cycles | Response | |||||||

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | (ACK) | |

| Start Condition? | Slave Address and Write Command | ||||||||

| Yes | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | (ACK) |

| Start Condition? | Control Register Address | ||||||||

| No | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | (ACK) |

| Start Condition? | Control Register bits | ||||||||

| No | Start Frequency Sweep | No Operation | Output Excitation Voltage² | PGA Gain | Response | ||||

| 1 | 0 | 1 | 1 | X¹ | D10 | D9 | 1 | (ACK) | |

¹ – Don't Care bit

² – 0 and 0 result in a 2V peak to peak range, 0 and 1 result in a 200 mV peak to peak range, 1 and 0 result in a 400 mV peak to peak range, 1 and 1 result in a 1V peak to peak range

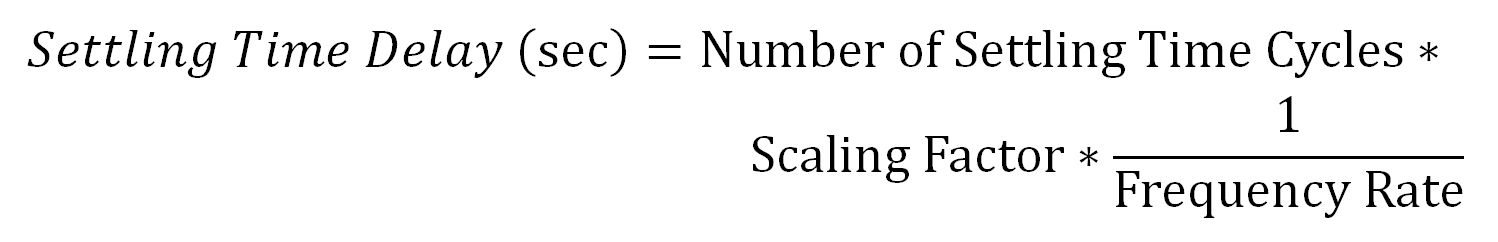

Naturally, some time is required for the DFT to be performed on the received data. Users can continuously poll the Status register to determine when the DFT is complete or can wait a calculated amount of time based on the number of Settling Time cycles before confirming the DFT is complete. The equation used to calculate the settling time is provided below:

Settling Time Calculation

| Start Condition? | Slave Address and Read Command | ||||||||

|---|---|---|---|---|---|---|---|---|---|

| Yes | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | (ACK) |

| Start Condition? | Status address 0x8F | ||||||||

| No | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | (ACK) |

| Start Condition? | Read bits | ||||||||

| No | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | (ACK) |

If bit D2 is at a logic level high voltage state, this indicates that the DFT is complete and the data present in the Real and Imaginary data registers are valid, allowing users to perform a block read on the two 16-bit registers.

| Start Condition? | Slave Address and Write Command | ||||||||

|---|---|---|---|---|---|---|---|---|---|

| Yes | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | (ACK) |

| Start Condition? | Pointer command | ||||||||

| No | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | (ACK) |

| Start Condition? | Real Data address 0x94 | ||||||||

| No | 1 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | (ACK) |

| Start Condition? | block read command | ||||||||

| No | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | (ACK) |

| Start Condition? | Desired number of bytes is 4 | ||||||||

| No | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | (ACK) |

| Start Condition? | Slave Address and Read Command | ||||||||

| Yes | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | (ACK) |

| Start Condition? | Byte 1 of Real Data | ||||||||

| No | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | (ACK) |

| Start Condition? | Byte 2 of Real Data | ||||||||

| No | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | (ACK) |

| Start Condition? | Byte 1 of Imaginary Data | ||||||||

| No | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | (ACK) |

| Start Condition? | Byte 2 of Imaginary Data | ||||||||

| No | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | (ACK) |

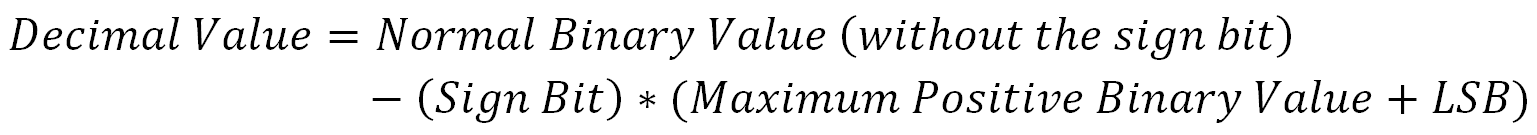

The data registers are arranged in a two's-complement format. A reference calculation to determine the decimal value of the data is provided below:

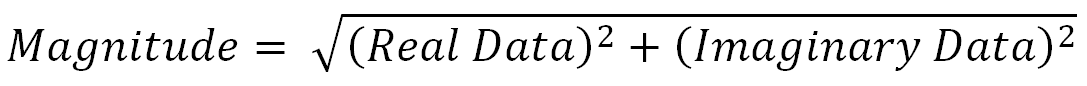

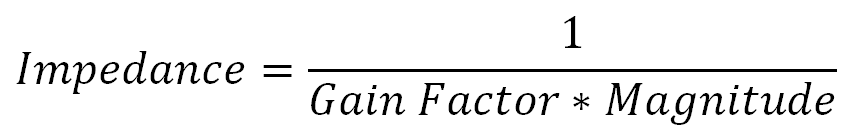

Once the data has been obtained, the gain factor can be calculated as follows:

Magnitude Calculation

Gain Factor Calculation

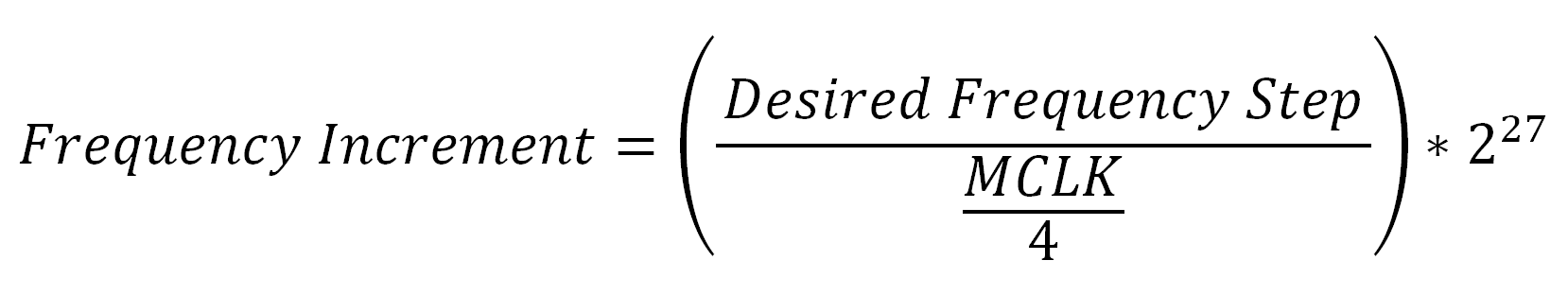

Once the gain factor has been determined, any other unknown impedance can then be calculated by the following equation:

Impedance Calculation

The calculated gain factor will remain valid for as long as the following parameters are not changed:

- Current-to-voltage gain setting resistor (unlikely to change unless the resistor is physically removed from the Pmod)

- Output Excitation voltage

- PGA gain

Calculating the Step Frequency

Calculating the Phase

Calculating the phase……to be added in the future since I decided to keep working on other reference manuals. Until then please look at Measuring the Phase Across an Impedance section in the AD5933 Reference Manual starting on page 19.

Commonly Used Registers and Commands

A list of commonly used Registers and Commands as well as some of their commonly used values taken from the AD5933 datasheet starting from page 23 is provided below:

| Function | Register Address/Value | Corresponding Bit Stream |

|---|---|---|

| Initialize with Start Frequency | 0x80 | 0001 X1YY2Z3 |

| Start Frequency | 0x80 | 0010 X1YY2Z3 |

| Increment Frequency | 0x80 | 0011 X1YY2Z3 |

| Repeat Frequency | 0x80 | 0100 X1YY2Z3 |

| Standby Mode | 0x80 | 1011 X1YY2Z3 |

| Set the Start Frequency | 0x82 | 24 bits representing the Start Frequency Code |

| Set the Increment Frequency | 0x85 | 24 bits representing the Frequency Increment |

| Set the Number of Increments | 0x88 | D15-D9 are don't cares, D8-D0 is the 9-bit word representing the number of increments |

| Set the number of Settling Time Cycles | 0x8A | D15-D11 are don't cares, D10-D94, D8-D0 is the 9-bit word representing the number of Settling Time Cycles |

| Check the Status of the Pmod | 0x8F | When bit D1 is set, the real/imaginary data in their respective registers are valid; when bit D2 is set, the frequency sweep has been completed |

| Real Data | 0x94 | 16 bits representing the measured Real Data |

| Imaginary Data | 0x96 | 16 bits representing the measured Imaginary Data |

| Address Pointer Command | 1011 0000 | Used to point to an Address before performing a block read/write |

| Block Read | 1010 0001 | Command to indicate a Block Write is going to be performed; the number of bytes to be read must be sent in the next byte |

| Block Write | 1010 0000 | Command to indicate a Block Write is going to be performed; the number of bytes to be write must be sent in the next byte |

Note1 – X is a don't care bit

Note2 – The two Y bits correspond to the output voltage range where '0' and '0' result in a 2V peak to peak range, '0' and '1' result in a 200 mV peak to peak range, '1' and '0' result in a 400 mV peak to peak range, '1' and '1' result in a 1V peak to peak range

Note3 – Z is the PGA gain bit where '0' corresponds to a gain of 5 and '1' responds to a gain of 1

Note4 – '0' and '0' leave the number of Settling Time Cycles as is, '0' and '1' double the set number of Settling Time Cycles, '1' and '0' is reserved, '1' and '1' quadruple the number of Settling Time Cycles

Size of parts needed for External Oscillator

Users can load their own crystal oscillator from the recommended packages on the PmodIA schematic. To do so, users likely need to change out the capacitors C7 and C11 and the resistor R8. The package size for both of the capacitors is 0603 and the package size for the resistor is 0402.