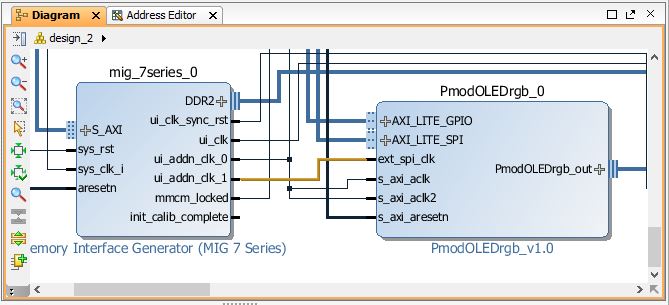

5.1) The PmodOLEDrgb requires a 50MHz ext_spi_clk, so we must generate this clock from the MIG (in a Microblaze design) or from the Zynq processor(in a Zynq design).

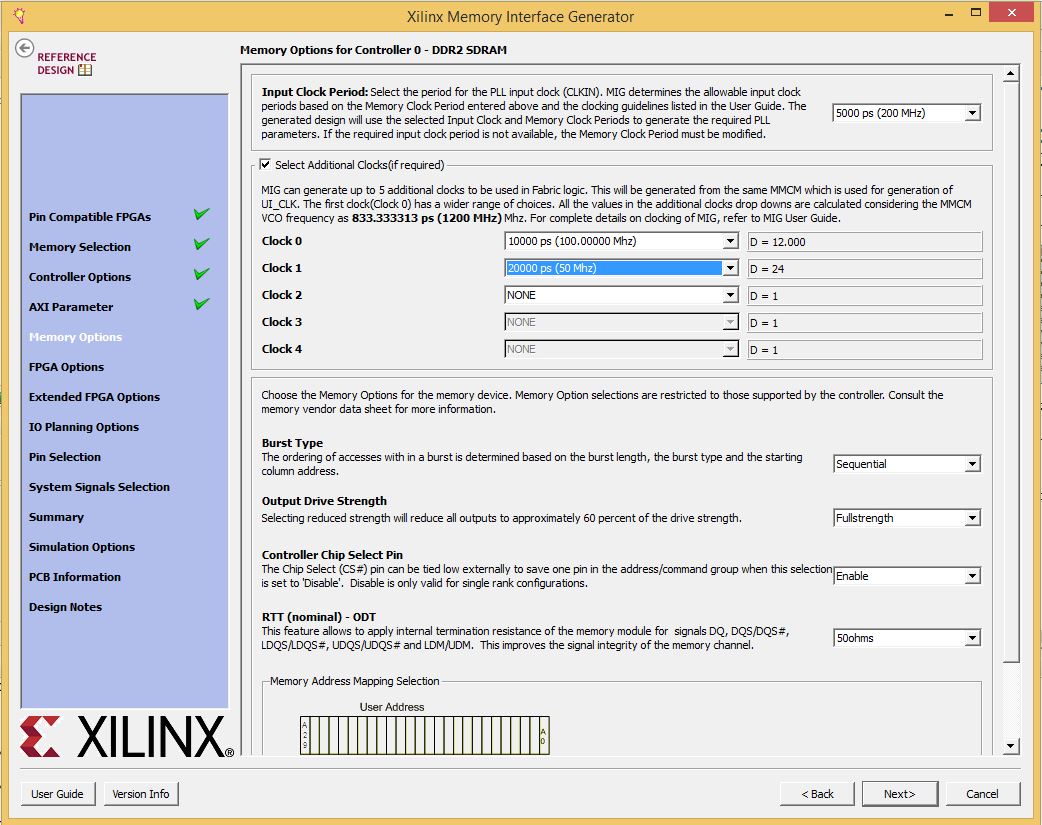

Microblaze: Double click the mig_7series block to re-customize it. In the Xilinx Memory Interface Generator window, keep clicking Next until you see Select Additional Clocks (shown below). Click this box and select a 50MHz or less clock from the drop down list.

When finished, keep clicking Next. When you reach the pin selection screen, click Validate and then OK. Keep clicking Next. Click Accept on the license agreement screen, then continue to click Next. Once you've reached the end, click Generate to regenerate your MIG block with your additional clocks.

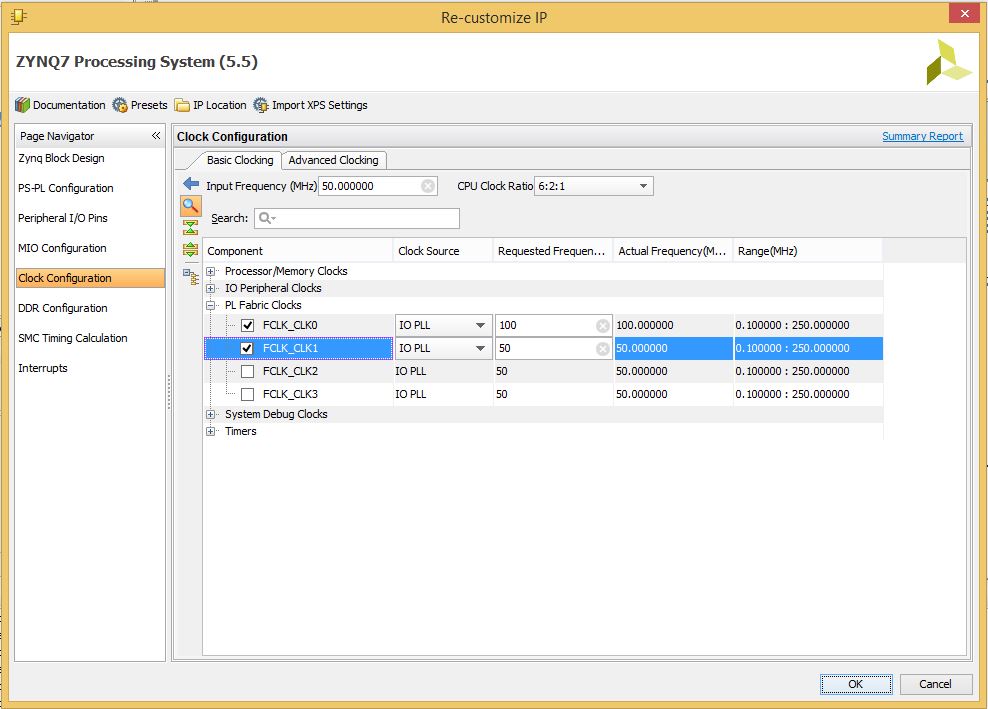

Zynq: Double click the ZYNQ block to re-customize it. In the menu to the left, click Clock Configuration. Open the PL Fabric Clocks drop down and check the next free FCLK_CLK and set the requested frequency to 50MHz or less. Click OK.