# CIO-DAS16/M1

1MHz 8 Channel 12 Bit Analog Input, Programmable Gain Queue 24 Digital I/O & Three 16 Bit Counter/Timers

#### **1 MHz DAS16/M1**

The CIO-DAS16/M1 multifunction analog and digital I/O board is the highest speed variation of the traditional DAS-16 architecture. The extra features of this newest DAS16 are:

- \* Blazing fast analog input of 1MHz continuous to MEGA-FIFO with sample size limited only by the size of memory on the MEGA-FIFO board.

- \* Pre-trigger and Post-trigger buffers of unlimited size managed by the hardware and software provide a seamless event driven sample set.

- \* Programmable 256 step channel/gain queue.

- \* DT-CONNECT interface for high speed direct transfer of analog data to MEGA-FIFO, array processors and other accessories.

- \* 24 digital I/O lines and three 16 bit counters, exactly like a CIO-DIO24/CTR3. An 82C55 digital I/O chip and an 82C54 counter/timer provide an array of interfacing options.

#### LOW COST - EXTRA FEATURES

The CIO-DAS16/M1 is one of the lowest cost megahertz A/D boards available. Compared with other high speed A/D boards the CIO-DAS16/M1 is less than half the price. By employing advanced features like DT-Connect, the CIO-MEGAFIFO and CIO-DAS16/M1 will out sample any other board we know of.

#### HUGESAMPLEBUFFER

The CIO-DAS16/M1 combined with a MEGA-FIFO can acquire sample sets of up to 128 Million Samples at full speed!

The CIO-DAS16/M1 employs the DT-Connect and MEGA-FIFO sample buffer board to acquire huge sample sets completely independent of PC bus rates or other simultaneous processes. High speeds and large sample sets are also possible direct to PC bus and PC memory because the CIO-DAS16/M1 uses a FIFO buffer and the REP-INSW command to transfer blocks at high speed into PC memory

#### **CONNECTOR COMPATIBLE**

The CIO-DAS16/M1 is connector compatible with the older, original DAS-16. The control registers are very similar to the CIO-DAS16/330i so adapting low-level drivers to the CIO-DAS16/M1 is a snap. Use the Universal Library language driver software and programs written for the CIO-DAS16/M1 will run other DAS-16 family boards as well.

#### **STREAMING SOFTWARE**

Streaming high speed samples to memory, RAM disk or hard disk is easy with the CIO-DAS16/M1's advanced architecture. The Universal Library includes modes for streaming data to files under program control.

#### **ANALOGINPUTS**

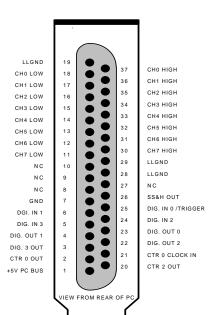

The analog input section of the CIO-DAS16/M1 has been designed for high speed, flexibility and accuracy in a number of configurations and ranges. The analog signals are brought on board by a standard 37 pin D connector directly to balanced multiplexors. The multiplexors are configured as 8 channels of differential input. Differential inputs can reject noise and ground loops (common mode voltages).

Signals are amplified by a programmable gain amplifier prior to conversion by the A/D converter. The possible gains and ranges and associated codes are shown in the table to the right.

An integral sample & hold captures the signal which is then converted by the A/D converter. The 12 bit A/D converter provides a resolution of 1 in 4096 parts of full scale.

The speed of data gathering may vary from less than 1Hz to 1MHz. Acquisition speed is dependent on the method of triggering and data transfer (and the PC speed if the MEGA-FIFO is not used).

| <u>METHOD</u>                           | MAX A/D Speed |

|-----------------------------------------|---------------|

| DT-Connect to MEGA-FIFO                 | 1MHz          |

| REP INSW to PC Memory                   | 330KHz - 1MHz |

| Polled by software                      | 4KHz-20KHz    |

| Interrupt Service Routine (no REP INSW) | 4KHz - 20KHz  |

# **DMA IS DEAD!** The REP INSW story.

REP INSW (Repeat Input String) is an x86 class CPU instruction which allows the PC to transfer large amounts of data using one instruction. The data is transferred at the maximum rate allowed by the bus. On a typical 286 AT, this rate is 2Mbyte/sec or 1 sample every microsecond.

In order to employ REP INSW the A/D board must have a FIFO buffer to accumulate sample data. The CIO-DAS16/M1 has a 1024 sample buffer. When it is half full (512 samples), an interrupt generated by the DAS16/M1 starts an interrupt service routine which executes the instruction REP INSW, transfers the data to PC memory and empties the FIFO buffer.

The data is transferred completely in the background and no unreasonable demands are placed on the PC's resources. For example, screen updates need not be suspended!

# GAIN & RANGE PROGRAMMING

No need to set switches to select an analog input range. The analog input range is fully programmable. A programmable gain queue controls both the unipolar/bipolar setting and the amplification of the analog input signal.

The gain/range control byte is located at BASE + 11:

| D7    | D6  | D5 | D4 | D3 | D2  | D1  | D0  |

|-------|-----|----|----|----|-----|-----|-----|

| Range | U/B | G1 | G0 | X  | Ch2 | Ch1 | Ch0 |

CHANNEL: The channel is set by bits Ch2-Ch0. Valid values are 0-7 for 8 channel, differential mode. For example, Ch2=1, Ch1=0, Ch0=0, then channel 4 is selected.

RANGE = The A/D chip input range, either 10V full scale or 20V full scale. 0 = 10V, 1 = 20V.

U/B = Unipolar or Bipolar ranges. 0 = Bipolar, 1 = Unipolar.

G1 G0 = the gain of the input amplifier. 0.0 = X1. 0.1 = X2. 1.0 = X4. 1.1 = X8.

Input Ranges

+/-10V +/-5V +/-2.5V +/-1.25V +/-0.625V

$0 \text{ to } 10 \text{V} \qquad 0 \text{ to } 5 \text{ V} \qquad 0 \text{ to } 2.5 \text{V} \qquad 0 \text{ to } 1.25 \text{V}$

# **GAIN QUEUE PROGRAMMING**

The channel/gain queue may be loaded with a sequence of between 1 and 256 channel+gain (CGQ) codes. When an analog input run is started, data will be acquired from the channels in the order specified by the CGQ. The programmable gain amplifier will be switched to the appropriate gain for the channel selected.

After the CGQ is loaded with a sequence of up to 256 different channel/gain combinations, all A/D channel & gain control are derived from the CGQ. The CGQ is automatically restarted when the last CGQ entry written is reached. For example, if you load 6 CGQ steps into the CGQ, the 1st, 7th, 12th... A/D sample in a run is controlled by the 1st entry in the CGQ. In this manner, large sample runs may be precisely controlled.

# A/D SPECIFICATIONS

Channels A/D Type Conversion Time A/D Convert & Transfer Speed Out DT-Connect

REP-INSW to PC Memory Paced Interrupt Service Routine

Accuracy Integral Linearity Maximum Overvoltage Input Leakage Current Gain Drift Zero Drift

### **12 BIT**

8 Differential Subranging Flash AD1671 0.8uS

1MHz

800KHz (typical 486/66) 20KHz (typical 486/66)

0.01% +/- 1 LSB +/- 1 LSB +/- 35V Continuous 250 nA Max @ 25°C +/- 35 ppm/Deg C Max +/- 25 ppm/Deg C Max

#### HIGH-SPEED CONTROL REGISTER

The DAS16/M1 has a special control register. This register controls word/byte transfers, enables the DT-Connect interface, pre/post trigger enable and FIFO status.

D7 D6 D5 D4 D3 D2 D1 D0 DTC PTE F/O X X X X X

**DTC** = DT Connect enable. 0 = disable. 1 = enable a DT Connect "Master Out". Data is available as each A/D conversion is completed. The slave must reply before the next conversion is complete.

**PTE** = Post Trigger Enable. 0 = disable. 1 = Enable the post-trigger counter to demarcate the boundary between pre- and post- trigger data.

$\mathbf{F}/\mathbf{Q} = \text{FIFO}$  buffer status /CGQ Active. Read: 1 = Overrun. A logical OR of the fault conditions FIFO Full, DTC overrun and DMA overrun. 0 = no fault.

#### I/O & CONTROL REGISTER MAP

The CIO-DAS16/M1 uses 16 I/O addresses for registers which control triggering, A/D sample rate, channel/gain queue and transfer mode. An additional 8 registers control digital and counter I/O.

| I/O ADDR. FUNCTION R/W                | I/O ADDR. | FUNCTION R -/W             |

|---------------------------------------|-----------|----------------------------|

| BASE + 0 A/D Low Byte / Start A/D     | BASE + 8  | Q Counter 0 / Load         |

| BASE + 1 A/D High Byte / NA           | BASE + 9  | Q Counter 1 / Load         |

| BASE + 2 Counter Source Control       | BASE + A  | Q Counter 2 / Load         |

| BASE + 3 Digital 4 In / Digital 4 Out | BASE + B  | NA / 8254 Control          |

| BASE + 4 A/D Status / IR Clr          | BASE + C  | Counter 0 / Counter 0 Load |

| BASE + 5 Control Settings / Control   | BASE + D  | Counter 1 / Counter 1 Load |

| BASE + 6 CGQ Address                  | BASE + E  | Counter 2 / Counter 2 Load |

| BASE + 7 Gain & Range Queue           | BASE + F  | NA / 8254 Counter Control  |

| I/O ADDR. 24 DIGITAL I/O & 3 COUNTERS |           |                            |

| BASE + 400 PORT A , 82C55             | DASE : 40 | 04 CTR 0. 82C54            |

| BASE + 400 PORT B, 82C55              |           | 05 CTR 1, 82C54            |

| · · · · · · · · · · · · · · · · · · · |           |                            |

| BASE + 402 PORT C, 82C55              |           | 06 CTR 2, 82C54            |

| BASE + 403 82C55 CONTROL              | BASE + 40 | 07 82C54 CONTROL           |

#### STANDARD DAS16 ANALOG CONNECTOR

The 37 pin D connector on the CIO-DAS16/M1 is identical to that of the CIO-DAS16.

Of course, the pins which carry analog output signals on the CIO-DAS16 are no-connect (NC) on the DAS16/M1 board. These pins are left floating rather than tied to ground or some other signal. That way your existing cables and connections will be compatible.

Because of Computer Boards' strict adherence to standards, cables and all of your existing hookups are 100% compatible with the DAS16 connector in the 8 channel differential mode.

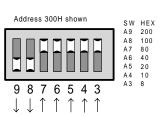

### **BASE ADDRESS**

The base address switch controls the block of I/O addresses occupied by the CIO-DAS16/M1. The CIO-DAS16/ M1 occupies 16 addresses. The 24 digital I/O and 3 counters use 8 addresses in the PC unused address space above 3FF Hex.

# 24 DIGITAL & 3 COUNTER FEATURES

24 Lines of TTL Digital I/O (8255) 3 Sixteen Bit Counters (8254) 10 MHz Oscillator on board **Internal Jumpers for Counter Chaining**

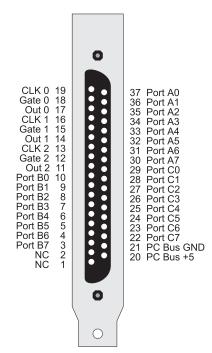

For applications which require multiple digital inputs and outputs, or counters, a second connector at the rear of the board provides access to one 82C55 DIO chip and one 82C54 counter. The configuration of the connector is identical to the CIO-DIO24/ CTR3. Digital I/O points may be used to sense contact closures or control relays.

Three, sixteen bit counters allow you to measure frequency or count events like the number of times a door opens, or items passing on a conveyor belt. The 8254 counter is easy to program and use from any language.

Please look at the connector diagram which shows the counter's input, gate and output pin assignments. If you would like to learn more about the 8254 counter, Intel publishes a data sheet that you can obtain from their web site.

# DIGITAL & COUNTER SPECIFICATIONS

#TTL Digital I/O Logic low level Logic high level Output low sink current Output high source current 8254COUNTER

Type - Fully programmable Control - TTL Level Max Input Frequency

24 as 3, 8 bit ports -0.5 to 0.8 V 2.0 to 5.5 V 0.4V @ 2.5mA 3.0V @ -2.5mA

16 Bit Down Counter Gated Input 10MHz - On board Osc

**CONNECTOR PIN-OUT OF BP40-37**

# **DIGITAL** I/O CONNECTOR

The connector carries 24 digital I/O lines and +5V from the PC power, or for the CTR3 board, plus the counter inputs and outputs.

The 8255 has 24 I/O lines. The chip is configured as 3 ports. Two ports, A & B, are 8 bits wide. Port C may be an 8 bit port or two 4 bit ports.

Individual ports may be configured as Input or Output and are written to and read from as a unit.

Counter inputs, gates and outputs may be controlled or chained at the connector, or inboard on a counter chaining jumper.

# UNIVERSAL LIBRARY DOS & Windows- Language Libraries

Programmers will appreciate the easy to use programming library, The Universal Library. It is universal in two ways. Universal functional syntax for all boards means that the program does not change no matter which A/D board you use as long as boards share common features. Universal language syntax means that the code is easily understood in all the languages supported because the syntax is constant across all languages.

The full range of capability for the CIO-DAS16/M1 is supported and new languages are being added. Please see the data sheet for the UniversalLibrary

# VI Components Windows Language Libraries Plus VBx, OCX or ActiveX controls

VI Components are a collection of routines you use like tools to save time solving programming problems, like adding graphics or analysis to your programs.

Solve Regression & Simultaneous equations. Do FFTs, matrix math or curve fitting. Display the results with charting graphics or 3 D plotting routines.

Please see the data sheet for VI Components.

# DT Connect<sup>TM</sup> High Speed Board-to-Board Interface

High speed transfers of data from the data acquisition board to special function boards, such as array processors or large sample buffers are best handled by dedicated interboard interfaces. Several such interfaces have been proposed by data acquisition vendors and one, DT-Connect has emerged as a standard.

Shown here is a high speed array processor connected to the CIO-DAS16/M1. A number of vendors subscribe to the DT-Connect standard for interboard communication because large blocks of data may be transferred at rates up to 10,000,000 Bytes/Sec independent of the PC bus

#### **MEGA-FIFO HUGE SAMPLE BUFFER**

Some 1MHz plus A/D boards come with a 1Mega Sample (MS) buffer on board, others can hold as much as 4MS. Only the CIO-DAS16/M1 can store up to 128 million samples completely independent of PC memory. Imagine 2MS, 8MS, 32MS or 128MS - full speed - fully independent!

Because the MEGA-FIFO gets data from the A/D board over the DT-Connect interface and not through the PC bus, transfer speeds are unaffected by PC overhead. Likewise, the A/D system does not slow down the PC which may be number crunching, painting graphics or moving data across networks.

#### Populate the MEGA-FIFO with Standard SIMMs

The MEGA-FIFO is sold without memory because you may have older 256K or 1M SIMMs stored in a drawer somewhere; the same as you would use in a PC. If you do not, you can buy standard 80nS SIMMs from a number of sources and the price is always falling. The MEGA-FIFO holds 16 SIMMs. Populate as follows with 256K SIMMs for 2MS, 1MBs for 8MS, 4MBs for 32MS or 16MBs for 128 Million Samples of A/D buffer!

# **ORDERING GUIDE**

1MHz Max Analog Input for AT/386 bus CIO-DAS16/M1

128 MEGA Sample Buffer Board MEGA-FIFO Sold without memory - Takes 256K, 1M, 4M, 16M SIMMs

Universal Library Programming Language Library UNIV-LIBRARY

Screw Terminal Boards

16" X 4" all signals from one 37 D plus proto area.CIO-TERMINAL4" X 4" all signals from one 37 D connector.CIO-MINI3716" X 4" all signals from one 37D, Spade Lug Terminals.CIO-SPADE50

Cables

40 Pin connector to D37 backplate BP40-37

2 foot ribbon cable, 37 conductor, female connectors. C37FF-2

'N' foot ribbon cable, 37 conductor, female connectors. C37FF-N

5 foot shielded cable, molded female connectors, 37 cond. C37FFS-5

10 foot shielded cable, molded female connectors, 37 cond. C37FFS-10

Measurement Computing Corporation 10 Commerce Way Suite 1008 Norton, Massachusetts 02766

(508) 946-5100 Fax: (508) 946-9500

E-mail: info@mccdaq.com

www.mccdaq.com