# 7210-TQFP-R

IEEE 488.2 Controller chip - replacement for NEC µPD7210

# 7210-TQFP-R

- RoHS-compliant

- Pin-compatible with NEC μPD7210

- Software-compatible with NEC μPD7210

- Low power consumption

- Meets all IEEE 488.2 requirements:

- $\circ$  Bus line monitoring

- $\circ$  Preferred implementation of requesting service

- $\circ$  Sends no messages when there are no listeners

- Performs all IEEE 488.1 interface functions SH1, AH1, T5 or TE5, L3 or LE3, SR1, RL1, PP1, PP2, DC1, DT1, C1, C2, C3, C4, C5

- Reduces driver overhead

#### Overview

Measurement Computing Corporation's 7210-TQFP-R is a 44-pin DIP replacement part for the NEC  $\mu$ PD7210. The 7210-TQFP-R is 100% register-compatible and pincompatible with the NEC  $\mu$ PD7210 on power up. The 7210-TQFP-R performs all of the interface functions defined by the ANSI/IEEE Standard 488.1-1987, and it meets the additional requirements and recommendations of ANSI/IEEE Standard 488.2-1987. The 7210-TQFP-R performs complete IEEE 488 talker, listener, and controller functions.

On power up, the 7210-TQFP-R contains the complete register set of the NEC  $\mu$ PD7210, but can perform complete IEEE 488.2 controller functions through software.

If you are an instrument developer, you can take advantage of IEEE 488.2 with minimal software modifications yet keep the 44-pin hardware configuration. The default clock input is 8 MHz, but increased performance is available from the 7210-TQFP-R through software-selectable input values up to 20 MHz.

If you are an IEEE 488 instrument manufacturer looking for alternatives to existing NEC  $\mu$ PD7210 chip suppliers or planning to upgrade your designs to IEEE 488.2 without hardware changes, consider using the 7210-TQFP-R. Because the 7210-TQFP-R accepts faster clock inputs, performance increases without many firmware changes.

- Does not lose a data byte if ATN is asserted while transmitting data

- Static interrupt status bits that do not clear when read

- Programmable data transfer rate

- (T1 delays of 350 ns, 500 ns, 1.1 μs, and 2 μs)

- Automatic EOS and/or NL message detection

- Direct memory access (DMA)

- Automatically processes IEEE 488 commands and reads undefined commands

- Programmable compatible with bus transceivers (T1, National Semiconductor, Motorola, and Intel)

- TTL-compatible CMOS device

- Programmable clock rate up to 20 MHz

#### General

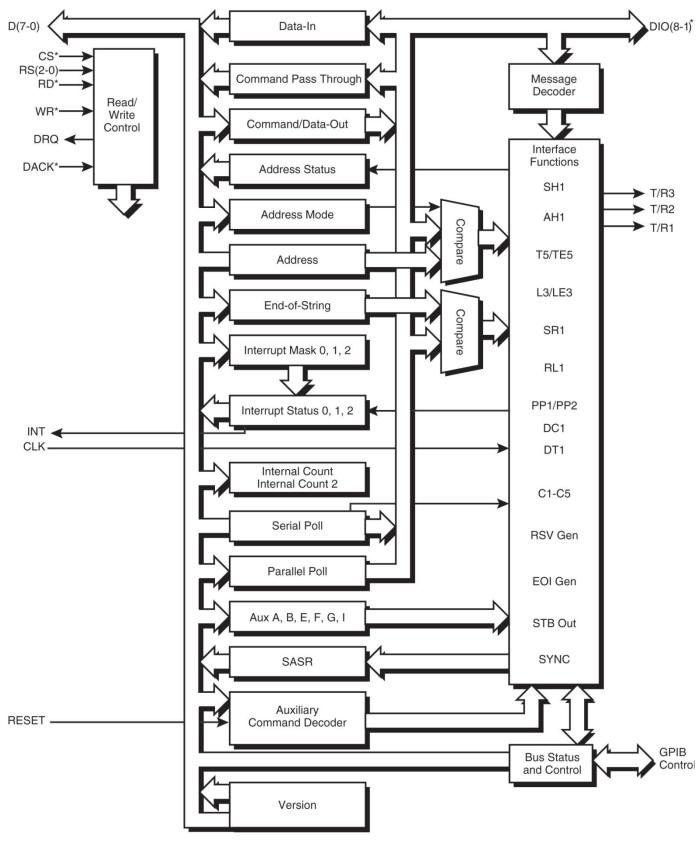

The 7210-TQFP-R manages the IEEE 488 bus. You program the IEEE 488 bus by writing control words into the appropriate registers. CPU-readable status registers supply operational feedback. The 7210-TQFP-R mode determines the function of these registers. When in 7210 mode, the registers resemble the  $\mu$ PD7210 register set with additional registers that supply extra functionality and IEEE 488.2 compatibility. In this mode, the 7210-TQFP-R is completely pin-compatible with the NEC  $\mu$ PD7210. Figure 1 shows the key components of the 7210-TQFP-R.

#### **RoHS Compliance**

The 7210-TQFP-R is available from MCC as a RoHScompliant chip. The chip is marked with an e3 inside an ellipse to indicate a matte pure tin finish on the leads, in accordance with the marking recommendations defined in JEDEC JESD97.

The RoHS-compliant 7210-TQFP-R meets industry requirements for baking and maximum solder reflow temperature. The baking requirements are outlined in JEDEC J-STD-033. MCC recommends using the solder reflow profile as shown in IPC/JEDEC J-STD-020C with a peak temperature of 260 °C, the maximum temperature they can withstand.

#### **Ordering Information**

| RoHS-compliant chip | MCC Part number |

|---------------------|-----------------|

| 44-pin LQFP package | 7210-TQFP-R     |

### **Block Diagram**

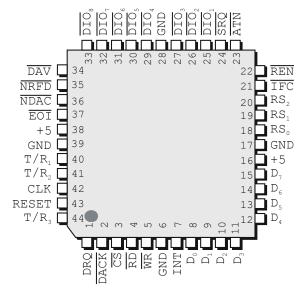

# **Pin Descriptions**

The following table describes the 7210-TQFP-R pins.

#### **Pin Identification**

#### Table 1. 7210-TQFP-R pin configuration

| Pin #         | Mnemonic                                            | I/O | Description                                                                                                                                                                             |  |  |  |  |

|---------------|-----------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1             | DRQ                                                 | 0   | DMA Request. Requests data transfer. Becomes low on input of DMA acknowledge signal DACK.                                                                                               |  |  |  |  |

| 2             | DACK                                                | I   | <b>DMA Acknowledge</b> . (Active low) Signal connects the computer system data bus to the data register of the 7210-TQFP-R.                                                             |  |  |  |  |

| 3             | CS                                                  | Ι   | Chip Select. (Active low) Enables access to the register selected by RS <sub>0</sub> -RS <sub>2</sub> (read or write operation).                                                        |  |  |  |  |

| 4             | RD                                                  | I   | Read. (Active low) Places contents of read register specified RS <sub>0</sub> -RS <sub>2</sub> on D <sub>0</sub> -D <sub>7</sub> (computer bus).                                        |  |  |  |  |

| 5             | WR                                                  | I   | Write. (Active low) Writes data on D <sub>0</sub> -D <sub>7</sub> into the write register specified by RS <sub>0</sub> -RS <sub>2</sub> .                                               |  |  |  |  |

| 6, 17, 28, 39 | GND                                                 |     | Ground                                                                                                                                                                                  |  |  |  |  |

| 7             | INT                                                 | 0   | <b>Interrupt Request</b> . (Active high/low) Becomes active due to any 1 of 13 internal interrupt conditions (unmasked). Active state software configurable. Active high on chip reset. |  |  |  |  |

| 8-15          | D <sub>0</sub> -D <sub>7</sub>                      | I/O | Data Bus. 8-bit bidirectional data bus for interface to the computer system.                                                                                                            |  |  |  |  |

| 16, 38        | +5 (V <sub>CC</sub> )                               | I/O | +5 VDC (±5%)                                                                                                                                                                            |  |  |  |  |

| 18-20         | RS <sub>0</sub> -RS <sub>2</sub>                    | I   | Register Select. These lines select one of eight read (write) registers during a read (write) operation.                                                                                |  |  |  |  |

| 21            | IFC                                                 | I/O | Interface Clear. Control line used for clearing the interface functions.                                                                                                                |  |  |  |  |

| 22            | REN                                                 | I/O | Remote Enable. Control line used to enable remote operation of the devices.                                                                                                             |  |  |  |  |

| 23            | ATN                                                 | I/O | Attention. Control line which indicates whether data on DIO lines is an interface message or device dependent message.                                                                  |  |  |  |  |

| 24            | SRQ                                                 | I/O | Service Request. Control line used to request service from the controller.                                                                                                              |  |  |  |  |

| 25-33         | $\overline{\text{DIO}}_1 - \overline{\text{DIO}}_8$ | I/O | Data Input/Output. 8-bit bi-directional bus for transfer of message.                                                                                                                    |  |  |  |  |

| 34            | DAV                                                 | I/O | Data Valid. Handshake line indicating that data on DIO lines is valid.                                                                                                                  |  |  |  |  |

| 35            | NRFD                                                | I/O | Ready for Data. Handshake line indicating that device is ready for data.                                                                                                                |  |  |  |  |

| 36            | NDAC                                                | I/O | Data Accepted. Handshake line indicating completion of message reception.                                                                                                               |  |  |  |  |

| 37            | EOI                                                 | I/O | <b>End or Identity</b> . Control line used to indicate the end of multiple byte transfer sequence or to execute a parallel polling in conjunction with ATN.                             |  |  |  |  |

| 40            | T/R <sub>1</sub>                                    | 0   | Transmit/Receive Control. Input/output control signal for the GPIB bus transceivers.                                                                                                    |  |  |  |  |

| 41            | T/R <sub>2</sub>                                    | 0   | <b>Transmit/Receive Control</b> . The values of $T/R_2$ and $T/R_3$ are determined by the values of the Address Mode register bits TRM1, and TRM0.                                      |  |  |  |  |

| 42            | CLK                                                 | I   | <b>Clock</b> . 1 MHz to 20 MHz reference clock for generating the state change prohibit times $T_1$ , $T_6$ , $T_7$ , $T_9$ specified in IEEE Standard 488.2-1992.                      |  |  |  |  |

| 43            | RESET                                               | I   | Reset. Resets the 7210-TQFP-R to an idle state when high (active high).                                                                                                                 |  |  |  |  |

| 44            | T/R <sub>3</sub>                                    | 0   | Transmit/Receive Control. See T/R <sub>2</sub> (pin 41).                                                                                                                                |  |  |  |  |

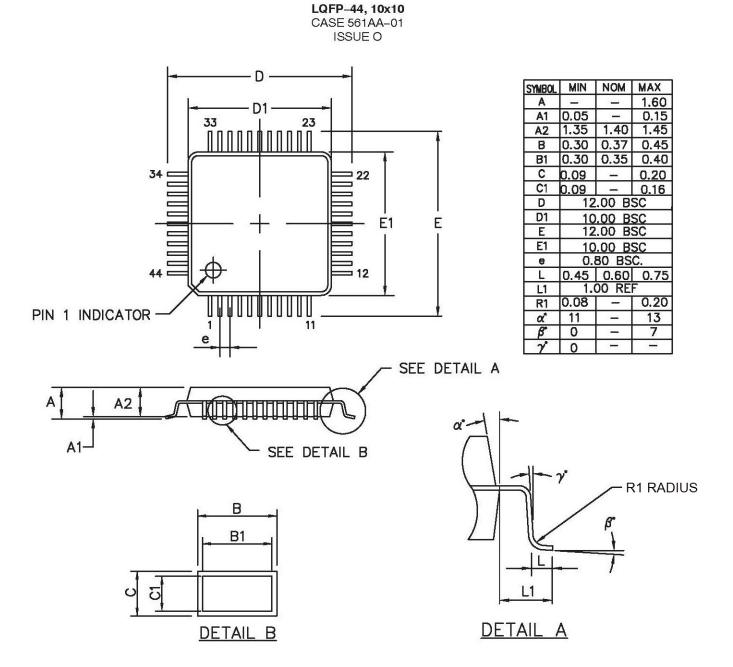

# **Mechanical Data**

Controlling dimensions are in millimeters.

#### 7210 Mode Registers

In 7210 mode, the 7210-TQFP-R registers include all the NEC  $\mu$ PD7210 registers plus two types of additional registers – extra auxiliary registers and paged-in registers. You write the extra auxiliary registers in the same way as standard  $\mu$ PD7210 auxiliary registers. Upon issuing an auxiliary page-in command, the paged-in registers appear at the same offsets as existing  $\mu$ PD7210 registers. At the end of the next CPU access, the chip pages out the paged-in registers. The following table lists the registers in the 7210 mode register set.

#### 7210 Register Set

| Register                                                                                                                                                                                       | Page<br>-In | A(2-0)      | WR*        | RD*       | CS*      | DACK*    |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|------------|-----------|----------|----------|--|

| Data-in                                                                                                                                                                                        | U           | 000         | 1          | 0         | 0        | 1        |  |

| Data-in                                                                                                                                                                                        | Х           | XXX         | 1          | 0         | Х        | 0        |  |

| Command/data-<br>out                                                                                                                                                                           | U           | 000         | 0          | 1         | 0        | 1        |  |

| Command/data-<br>out                                                                                                                                                                           | Х           | XXX         | 0          | 1         | Х        | 0        |  |

| Interrupt status <sup>1</sup>                                                                                                                                                                  | U           | 001         | 1          | 0         | 0        | 1        |  |

| Interrupt mask <sup>1</sup>                                                                                                                                                                    | U           | 001         | 0          | 1         | 0        | 1        |  |

| Interrupt status <sup>2</sup>                                                                                                                                                                  | U           | 010         | 1          | 0         | 0        | 1        |  |

| Interrupt mask <sup>2</sup>                                                                                                                                                                    | U           | 010         | 0          | 1         | 0        | 1        |  |

| Serial poll status                                                                                                                                                                             | Ν           | 011         | 1          | 0         | 0        | 1        |  |

| Serial poll mode                                                                                                                                                                               | Ν           | 011         | 0          | 1         | 0        | 1        |  |

| Version                                                                                                                                                                                        | Р           | 011         | 1          | 0         | 0        | 1        |  |

| Initial counter <sup>2</sup>                                                                                                                                                                   | Р           | 011         | 0          | 1         | 0        | 1        |  |

| Address status                                                                                                                                                                                 | U           | 100         | 1          | 0         | 0        | 1        |  |

| Address mode                                                                                                                                                                                   | U           | 100         | 0          | 1         | 0        | 1        |  |

| Command pass through                                                                                                                                                                           | N           | 101         | 1          | 0         | 0        | 1        |  |

| Auxiliary mode                                                                                                                                                                                 | U           | 101         | 0          | 1         | 0        | 1        |  |

| Source/acceptor status <sup>†</sup>                                                                                                                                                            | Р           | 101         | 1          | 0         | 0        | 1        |  |

| Address 0                                                                                                                                                                                      | Ν           | 110         | 1          | 0         | 0        | 1        |  |

| Address                                                                                                                                                                                        | Ν           | 110         | 0          | 1         | 0        | 1        |  |

| Interrupt status<br>0 <sup>†</sup>                                                                                                                                                             | Р           | 110         | 1          | 0         | 0        | 1        |  |

| Interrupt mask 0 <sup>†</sup>                                                                                                                                                                  | Р           | 110         | 0          | 1         | 0        | 1        |  |

| Address <sup>†</sup>                                                                                                                                                                           | Ν           | 111         | 1          | 0         | 0        | 1        |  |

| End-of-string                                                                                                                                                                                  | Ν           | 111         | 0          | 1         | 0        | 1        |  |

| Bus status <sup>†</sup>                                                                                                                                                                        | Р           | 111         | 1          | 0         | 0        | 1        |  |

| Bus control <sup>†</sup>                                                                                                                                                                       | Р           | 111         | 0          | 1         | 0        | 1        |  |

| Notes for the Page                                                                                                                                                                             | In colum    | าท:         |            |           |          |          |  |

| U = The page-in                                                                                                                                                                                | auxiliary   | command     | does no    | ot affect | the reg  | jister.  |  |

| <ul> <li>U = The page-in auxiliary command does not affect the register.</li> <li>N = The register offset is always valid except for immediately after a page-in auxiliary command.</li> </ul> |             |             |            |           |          |          |  |

| P = The register command.                                                                                                                                                                      | is valid o  | nly immed   | diately af | ter a pa  | ige-in a | uxiliary |  |

| The <sup>†</sup> symbol indic                                                                                                                                                                  | ates feat   | ures that a | are not a  | vailable  | in the p | uPD7210, |  |

such as register and auxiliary commands.

#### **DC Characteristics**

| Parameter                                                    | rameter Symbol Limits |      | Unit | Test              |                             |

|--------------------------------------------------------------|-----------------------|------|------|-------------------|-----------------------------|

|                                                              | -                     | Min  | Мах  |                   | Conditions                  |

| Voltage input<br>low                                         | VIL                   | -0.5 | +0.8 | V                 |                             |

| Voltage input<br>high                                        | VIH                   | +2.0 | VCC  | V                 |                             |

| Voltage output<br>low                                        | VOL                   | 0    | 0.4  | V                 |                             |

| Voltage output<br>high                                       | VOH                   | +2.4 | VCC  | V                 |                             |

| Input/output<br>leakage<br>current                           |                       | -10  | +10  | μΑ                | w/o internal<br>pull-up     |

| Input/output<br>leakage<br>current                           |                       | -200 | +200 | μΑ                | with<br>internal<br>pull-up |

| Supply<br>Current                                            |                       |      | 45   | mA                |                             |

| Output current<br>low (all pins<br>except T/R <sub>1</sub> ) | IOL                   | 2    |      | mA                | VOL=0.4 V                   |

| T/R <sub>1</sub>                                             | IOL                   | 4    |      | mA                | VOL=0.4 V                   |

| Input current<br>low/high                                    | IIL                   |      | -0.5 | mA                |                             |

| Output current<br>high                                       | IOH                   | -1   | mA   | V0H=VCC-<br>0.5 V |                             |

| Supply<br>voltage                                            | VCC                   | 4.75 | 5.25 | V                 |                             |

# Capacitance

TA<sub>0</sub> to 70 °C; V<sub>cc</sub>= 5 V  $\pm$ 5%

| Parameter             | Symbol | Limits |     | Unit | Test Conditions |

|-----------------------|--------|--------|-----|------|-----------------|

|                       |        | Min    | Max |      |                 |

| Input<br>capacitance  | Cin    |        | 10  | pF   |                 |

| Output<br>capacitance | Cout   |        | 10  | pF   |                 |

| I/O<br>capacitance    | CI/O   |        | 10  | pF   |                 |

# Absolute Maximum Ratings

| Test Conditions                             |  |  |  |  |  |

|---------------------------------------------|--|--|--|--|--|

| -0.5 to +6.0 V                              |  |  |  |  |  |

| -0.5 to VCC +0.5                            |  |  |  |  |  |

| 0 to +70 °C                                 |  |  |  |  |  |

| Storage temperature, -40 to +125 °C<br>TSTG |  |  |  |  |  |

|                                             |  |  |  |  |  |

cause permanent damage. The device is not meant to be operated under conditions outside the operational limits. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

# **AC Characteristics**

I

TA0 to 70 °C; Vcc= 5 V ±5%

| Parameter                                                                 | Sym.            | Limits |     | Unit | Test       |

|---------------------------------------------------------------------------|-----------------|--------|-----|------|------------|

|                                                                           |                 | Min    | Мах |      | Conditions |

| Address hold from<br>RD ↑ WR ↑                                            | t <sub>AH</sub> | 0      |     | ns   |            |

| Address setup to $\overline{RD} \downarrow$<br>$\overline{WR} \downarrow$ | t <sub>AS</sub> | 0      |     | ns   |            |

| Data float from RD ↑                                                      | t <sub>DF</sub> |        | 25  | ns   |            |

| Data delay from $\overline{RD} \downarrow$                                | t <sub>DR</sub> |        | 80  | ns   | DACK=0     |

| DRQ unassertion                                                           | t <sub>DU</sub> |        | 25  | ns   |            |

| Data delay from $\overline{\text{RD}}\downarrow$                          | t <sub>RD</sub> | 85     | ns  | CS=0 |            |

| RD recovery width                                                         | t <sub>RR</sub> | 120    |     | ns   |            |

| RD pulse width                                                            | t <sub>RW</sub> | 85     |     | ns   |            |

| Data setup to $\overline{\mathrm{WR}}$ $\uparrow$                         | t <sub>ws</sub> | 60     |     | ns   |            |

| Data hold from WR↑                                                        | t <sub>WH</sub> | 0      |     | ns   |            |

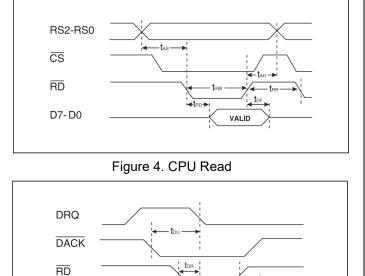

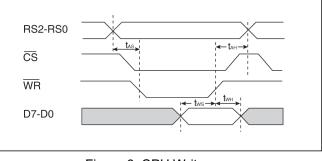

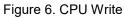

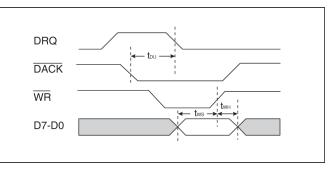

# Timing Waveforms

D7-D0

Figure 5. DMA Read

t⊳

VALID

Figure 7. DMA Write

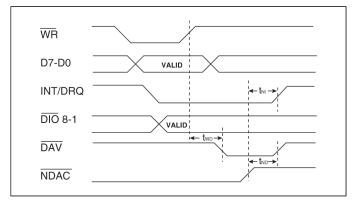

#### Source Handshake

| Parameter                                                                                               | Sym.            | Limits |       | Test Conditions                           |

|---------------------------------------------------------------------------------------------------------|-----------------|--------|-------|-------------------------------------------|

|                                                                                                         |                 | Min    | Мах   |                                           |

| $\overline{\text{NDAC}} \uparrow \text{to } \overline{\text{DAV}} \uparrow$                             | t <sub>ND</sub> |        | 40    |                                           |

| $\frac{\overline{NDAC} \uparrow \text{to } \overline{INT} \uparrow \text{or}}{\overline{DRQ} \uparrow}$ | t <sub>NI</sub> |        | 40    | INT (DO IE Bit = 1)<br>DRQ (DMAO Bit = 1) |

| $\overline{WR}$ $\uparrow$ to $\overline{DAV}$ $\downarrow$                                             | t <sub>WD</sub> | 2,000  | 2,125 | 2 µs T1<br>(8 MHz, 50% duty)              |

| $\overline{WR}$ $\uparrow$ to $\overline{DAV}$ $\downarrow$                                             | t <sub>WD</sub> | 1,125  | 1,250 | 1.1 μs T1<br>(8 MHz, 50% duty)            |

| $\overline{WR}$ $\uparrow$ to $\overline{DAV}$ $\downarrow$                                             | t <sub>WD</sub> | 500    | 625   | 500 ns T1<br>(8 MHz, 50% duty)            |

| $\overline{WR}$ ↑ to $\overline{DAV}$ ↓                                                                 | t <sub>WD</sub> | 375    | 500   | 350 ns T1<br>(8 MHz, 50% duty)            |

Figure 8. Source Handshake

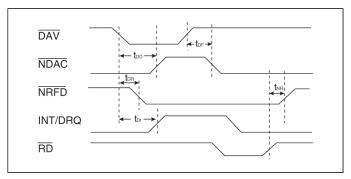

#### Acceptor Handshake

| Parameter                                                               | Sym.            | Limits |     | Test Conditions                          |

|-------------------------------------------------------------------------|-----------------|--------|-----|------------------------------------------|

|                                                                         |                 | Min    | Max |                                          |

| $\overline{\text{DAV}}\downarrow$ to $\overline{\text{NDAC}}\uparrow$   | t <sub>DD</sub> |        | 225 | 8 MHz, 50% duty                          |

| DAV ↑ to NDAC↓                                                          | t <sub>DD</sub> |        | 20  |                                          |

| DAV↓to INT↑or<br>DRQ↑                                                   | t <sub>NI</sub> |        | 116 | INT (DIIE Bit = 1)<br>DRQ (DMAI Bit = 1) |

| $\overline{\text{DAV}}\downarrow$ to $\overline{\text{NRFD}}\downarrow$ | t <sub>DR</sub> |        | 25  |                                          |

| RD↑ to NRFD↑                                                            | t <sub>NR</sub> |        | 30  | Read of DIR, not in<br>Holdoff state     |

Figure 9. Acceptor Handshake

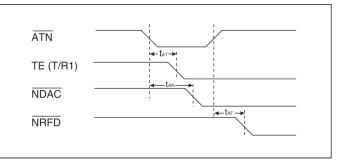

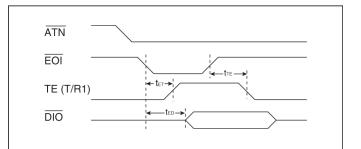

### **Response to ATN**

| Parameter                                                               | Sym.            | Limits |     | Test Conditions               |

|-------------------------------------------------------------------------|-----------------|--------|-----|-------------------------------|

|                                                                         |                 | Min    | Max |                               |

| ATN ↑ to NRFD ↓                                                         | $t_{\Delta F}$  |        | 35  | Acceptor handshake<br>Holdoff |

| $\overline{\text{ATN}}\downarrow$ to $\overline{\text{NDAC}}\downarrow$ | t <sub>AN</sub> |        | 35  | $AIDS \to ANRS$               |

| $\overline{\text{ATN}}\downarrow$ to $\overline{\text{TE}}\downarrow$   | t <sub>AT</sub> |        | 30  | $TACS\toTADS$                 |

#### **Parallel Poll**

| Parameter                                                                  | Sym.            | Limits |     | Test Conditions |

|----------------------------------------------------------------------------|-----------------|--------|-----|-----------------|

|                                                                            |                 | Min    | Мах |                 |

| EOI↓ to DIO valid                                                          | t <sub>FD</sub> |        | 90  | PPSS > PPAS     |

| EOI↓ to TE↑                                                                | t <sub>ET</sub> |        | 25  | PPSS > PPAS     |

| $\overline{\text{EOI}} \uparrow \text{to} \overline{\text{TE}} \downarrow$ | t <sub>TE</sub> |        | 25  | PPAS > PPSS     |

Figure 11. Parallel Poll

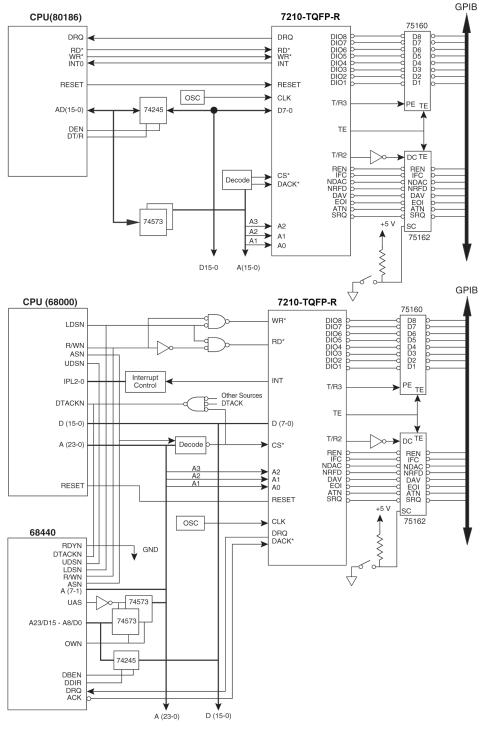

# **Typical System**

Figure 12. Typical CPU System with the 7210-TQFP-R

#### **Contact us**

Contact us if you need assistance in developing the interface to your particular system. Our engineering staff will work with you to ensure that your 7210-TQFP-R interface is simple, efficient and allows access to all chip features.

- Phone: 508-946-5100 and follow the instructions for reaching Tech Support

- Fax: 508-946-9500 to the attention of Tech Support

- Email: <u>techsupport@mccdaq.com</u>

Measurement Computing Corporation 10 Commerce Way Norton, Massachusetts 02766 (508) 946-5100 E-mail: <u>info@mccdaq.com</u> <u>www.mccdaq.com</u>

NI Hungary Kft H-4031 Debrecen, Hátar út 1/A, Hungary Phone: +36 (52) 515400 Fax: +36 (52) 515414 hungary.ni.com/debrecen