Arty Programming Guide

Overview

There are two ways you can program the Arty:

- JTAG

- Quad SPI Flash

This tutorial will walk you through what you need to know to get started on your projects and program your Arty FPGA board using both possible methods. It is recommended that you first complete the “Getting Started with Vivado” guide before continuing with this project.

Prerequisites

Skills

- Basic familiarity with Vivado

- This experience can be found by walking through our “Getting Started with Vivado” guide

Hardware

- Arty FPGA board

- Micro-USB cable

Software

- Vivado Design Suite 2015.1

- Newer/older versions can be used, but the procedure may vary slightly

Board Support Files

- Arty Support Files

- These files will describe GPIO interfaces on your board and make it easier to select your FPGA board and add GPIO IP blocks.

- Follow the Wiki guide: Vivado Board Files for Digilent 7-Series FPGA Boards on how to install Board Support Files for Vivado.

Downloads

Source Files – ZIP

Tutorial

1. Creating the Project

First we will need to create a project.

1.1) Open up Vivado and click Create New Project to open Vivado's New Project wizard.

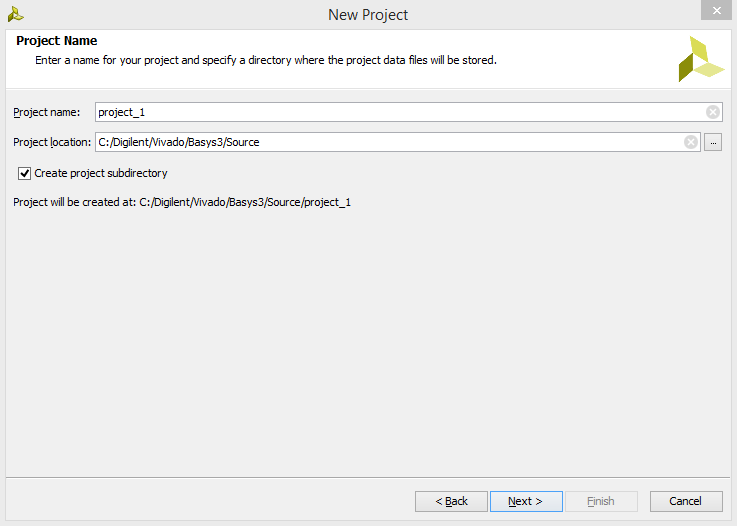

1.2) A new window will open up, click Next and you'll see the screen below. Name your project (no spaces!) and choose your project saving directory before clicking Next.

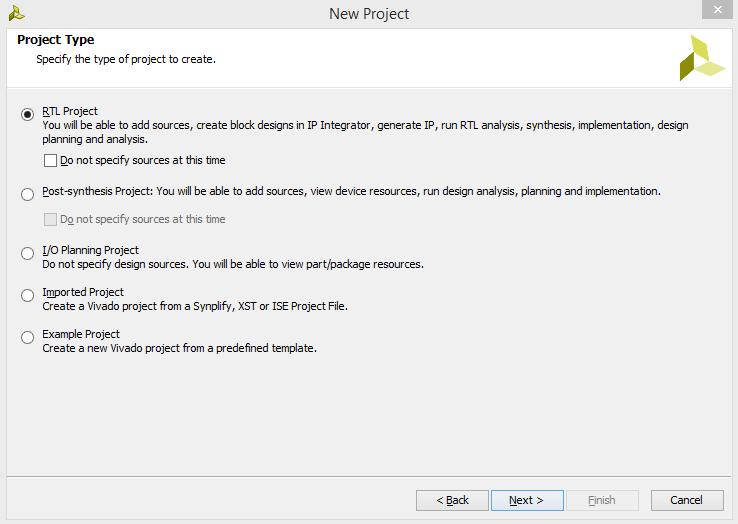

1.3) We will be building this project from the ground up and adding our own sources so we will want to create an RTL project. Select RTL Project and click Next.

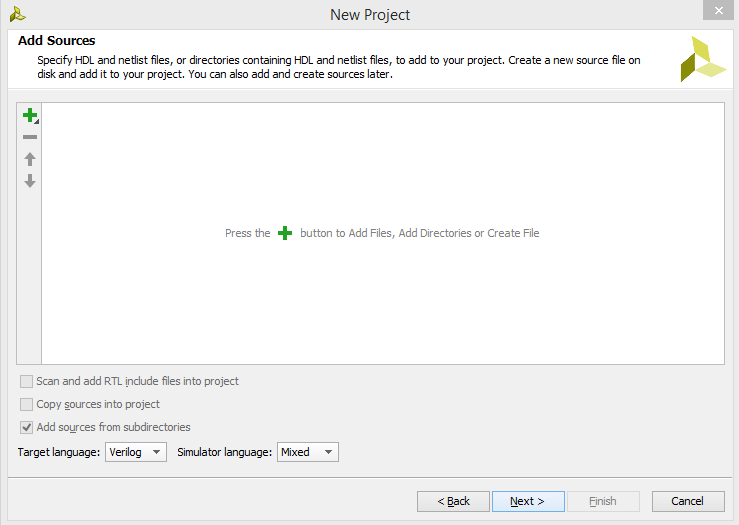

1.4) In this window, you can select any source files or directories that you'll want to use in your projects. We can also select which language we'll be programming in. For this project just keep the default settings. We'll be importing the pre-built Verilog files into our project so click the '+' sign in the center of the window, and navigate to where you saved the source files from before, select sw_led.v and click Ok. After selecting your source a series of check boxes should become active. Check mark “Copy sources into project”. If you do not check this box, Vivado will not create separate copies of your sources and place them within your project directory. Instead Vivado will read/modify directly from the source. Click Next to continue.

1.5) This window lets you choose existing IP (Intellectual Property) cores if you have them, but for this tutorial no IP's will be necessary. Click Next.

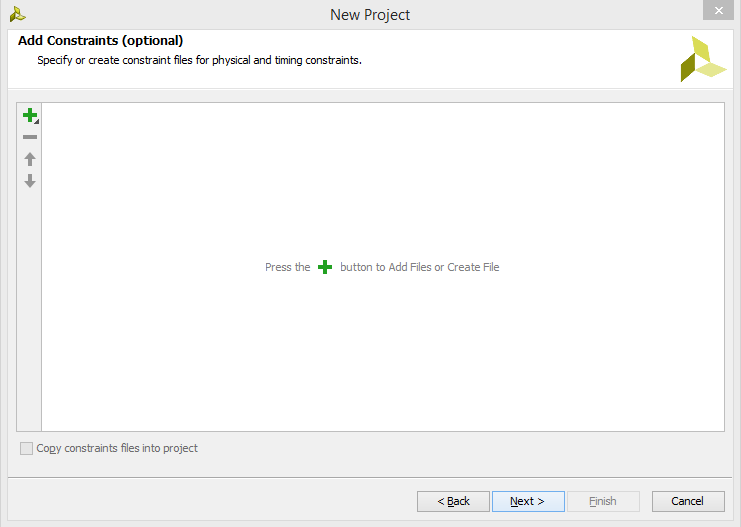

1.6) This is where we'll import our Xlilinx Design Constraints file (XDC) to map the HDL signals to the Artix-7 pins. Click on the '+' in the middle of the screen to add files, navigate to where you saved your Arty_sw_Demo.xdc file, select it, and click Next.

1.7) At this point Vivado will open up a part selection window. Select the Boards tab highlighted in orange below. If you installed the board files correctly, you should see a list of Digilent boards. Select the Arty and click Next.

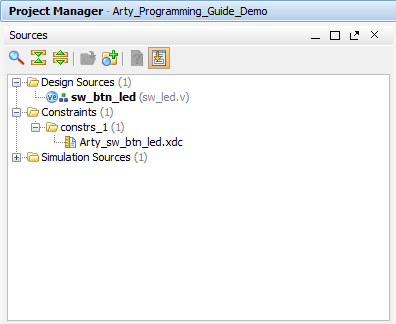

1.8) This will create your project and bring you to the Vivado project manager. You will see the files that you imported earlier in the Sources box.

You have now successfully imported you program files and configured your project to properly communicate with the Arty.

2. Creating Program File

For the three ways to program your Arty FPGA there are two file types available; .bit and .bin files. For a .bit file we can use the JTAG programming cable to load the bit file into the FPGA. Programming with a .bin file will use the QuadSPI to program the FPGA each time it is powered on. This means you will not have to reprogram it each time via a micro USB cable. The following steps bellow will get you all prepared to program your Arty.

2.1) In order to program the FPGA on startup we have to specify that we want to generate a .bin file. This can be done by clicking Tools→Project Settings→Bitstream. In this window we will check the box next to .bin_file. Now Vivado will create both a .bit, and .bin file when we generate a Bitstream.

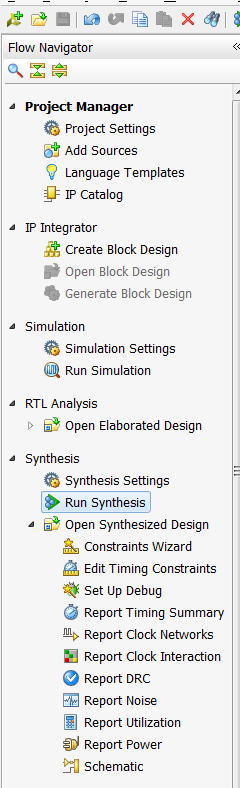

2.2) To begin, we will run the synthesis by clicking Run Synthesis beneath Synthesis in the Flow Navigator on the left side of Vivado.

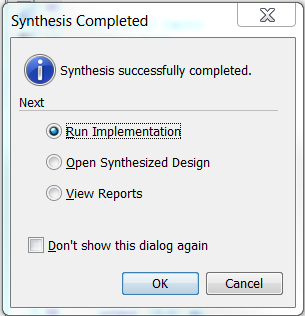

2.3) When the program finishes synthesizing your project, you will see the Synthesis Completed window below. Click Open Synthesized Design and then press Ok.

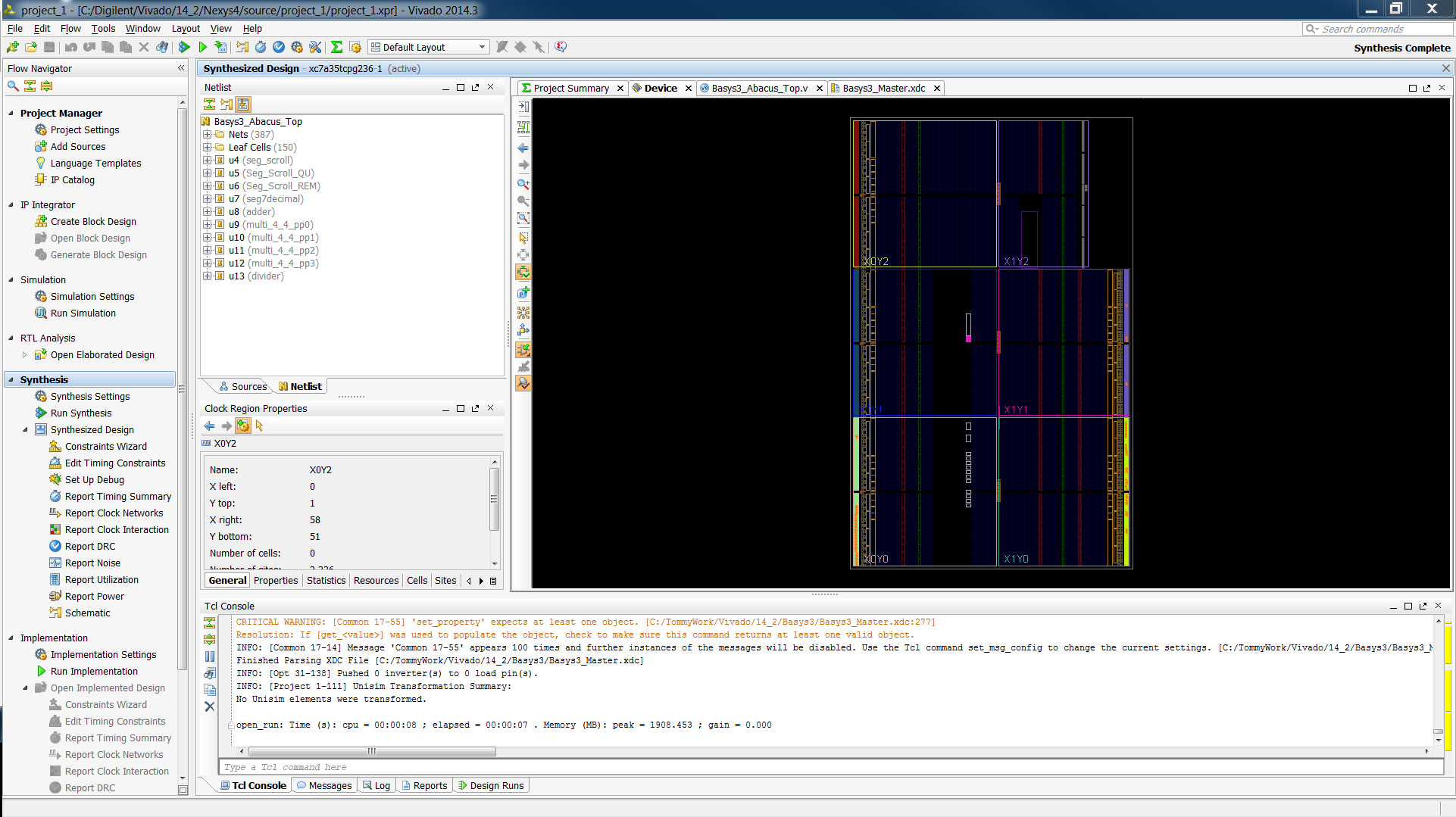

2.4) You should now see your Synthesized Design in the window to the right. It should look like this:

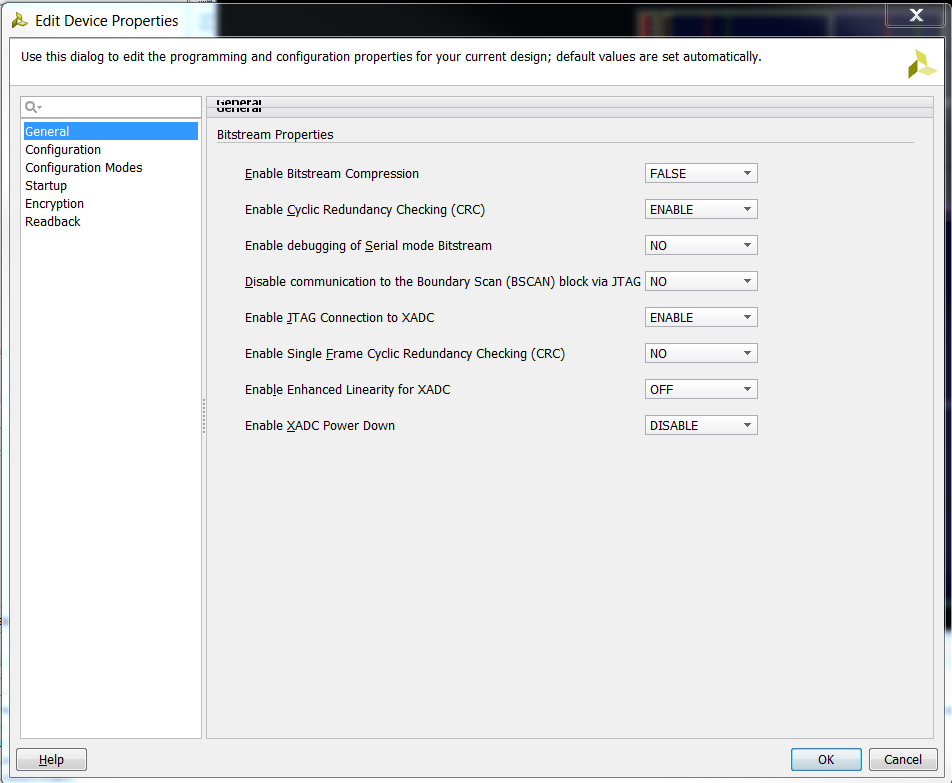

2.5) To improve programming speed of our .bin file, in the main toolbar select Tools→Edit Device Properties. Under General, set Enable Bitsream Compression to “TRUE”.

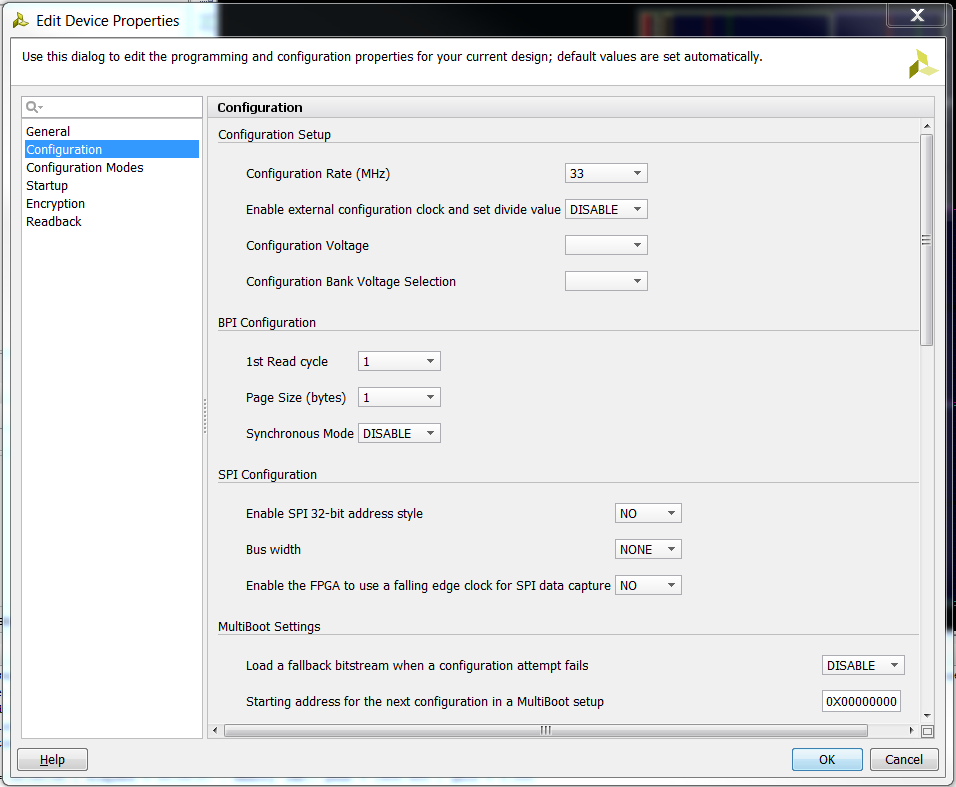

2.6) Under Configuration, set Configuration Rate (Mhz) to “33”.

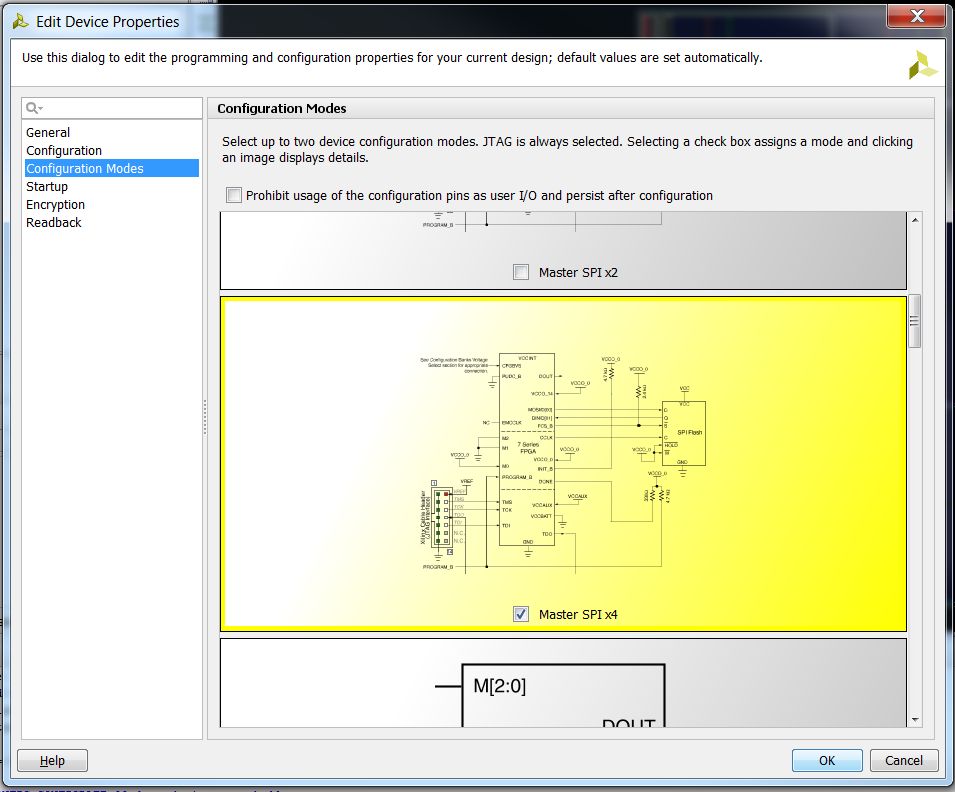

2.7) Under Configuration Modes, select Master SPI x4

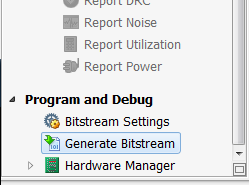

2.8) Click Ok, save your synthesized design (Ctrl+S) and then click Generate Bitstream in the Flow Navigator on the left side.

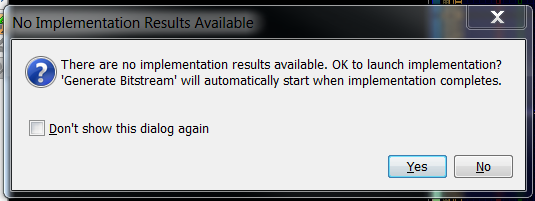

2.9) This will open a box stating that you have not implemented your design. Click Ok.

2.10) Vivado will begin generating your bit and bin files. When completed Vivado will show you this box. Feel free to select Open Implemented Design, or View Reports but you can also just cancel to continue with the guide.

At this point you have successfully created a .bit and .bin file that are ready to program the Arty. As said previously there are two ways to program the Arty FPGA board, and we will be walking through both one of them below.

3. Programming the Arty using JTAG

JTAG is primarily used as a programming, debugging, and probing port and communicates through the micro-USB port. This makes interfacing with the Arty easy because the micro-USB connection both supplies power to your board, and the ability to program it.

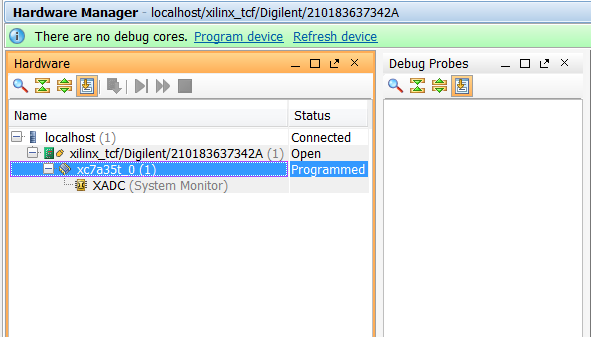

3.1) First, make sure that JP1 does not have a jumper and that the Arty is plugged into your computer via micro-USB cord. Once the board is plugged in you should see something like this.

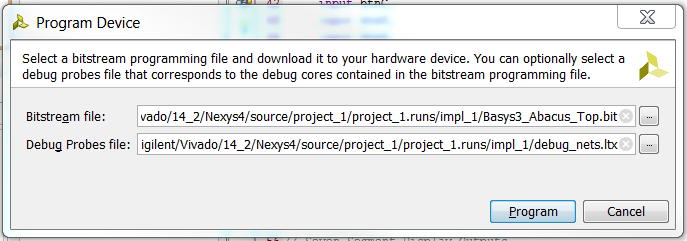

3.2) Click Program device (in the green bar) then xc7a35t_0, select your .bit file in the bitstream file box, and click Program.

This will program your Arty through the JTAG connector. Once the programming window is closed go ahead and test out your board. Each slide switch at the bottom of your board should now toggle its respective LED on and off.

4. Programming the Arty using Quad SPI

Quad SPI Flash is a non-volatile memory that the Arty's FPGA chip looks at on every startup. If Quad SPI is flashed then the FPGA will program itself with the contents found in Quad SPI's flash memory. This method of programming your board is great when you have a final project that you would like to demo or display that doesn't need to be edited and therefore reprogrammed.

4.1) Make sure the jumper is on JP1.

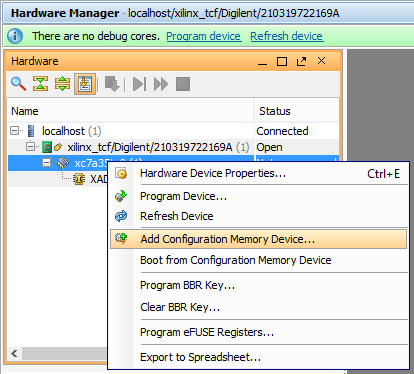

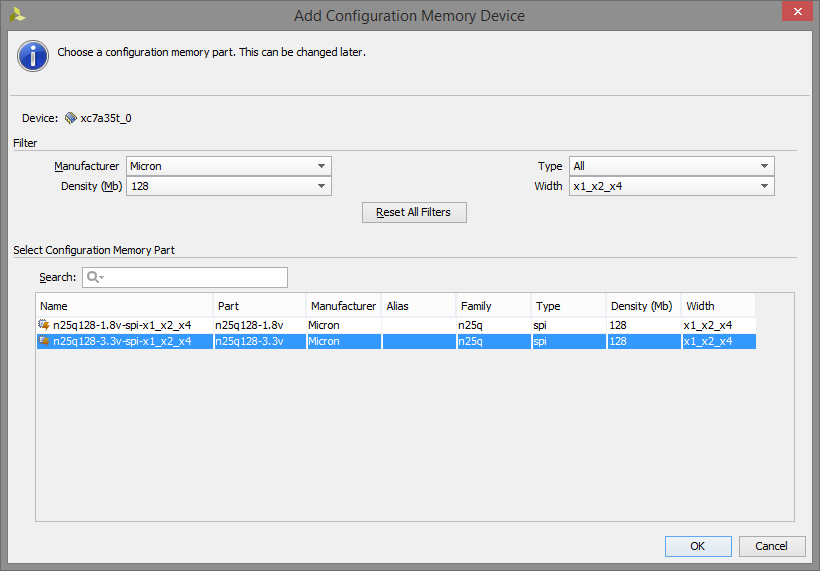

4.2) In the Hardware Manager window, under hardware right click your device and click Add Configuration Memory Device…

4.3) This window will pop up. Search for “Micron” and select n25q128-3.3v-spi-x1_x2_x4. Click OK on the next window asking if you want to program the configuration memory device.

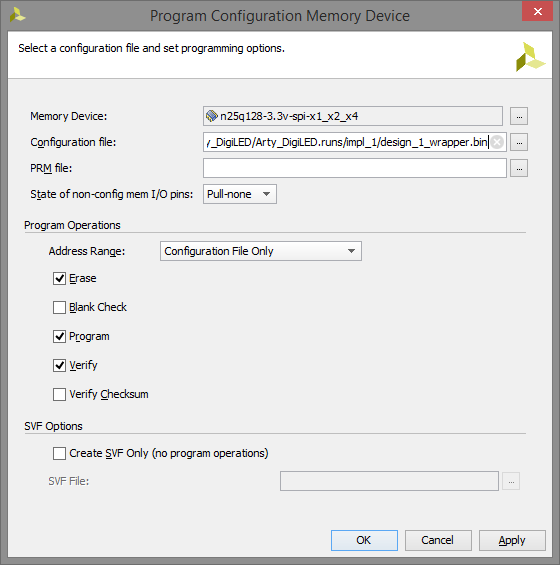

4.4) Select the .bin file where it asks for a configuration file and finally click OK.

Vivado will now erase the old configuration file, and reprogram your Arty's memory with the demo file. From now on, at each power up of the board, the demo will run, until a new reprogramming of the memory of FPGA.