# Introduction to FPGA

Adam Taylor

#### **Xilinx Tools and Frameworks**

#### **VitisAI**

Enables the implementations of machine learning inference, using Tensor Flow, Caffe and PyTorch. \*Requires a SoC/RFSoC/Alveo

#### Vitis

Embedded and accelerated SW development. Used to develop software solutions for MicroBlaze, Arm R5, A9, A53 and A72.

#### **Petalinux**

Embedded Linux solutions

#### **PYNQ**

Python framework for rapid prototyping on SoC/RFSoC/Alveo

#### Vitis / Vivado HLS

High Level Synthesis tool supporting C/C++/OpenCL

#### Vivado

Design Capture and implementation for the base platform

| Session 1       | Session 2     | Session 3 | Session 4    |

|-----------------|---------------|-----------|--------------|

| Introduction to | Processing in | Embedded  | Accelerating |

| Xilinx FPGA     | Xilinx FPGA   | Linux     | Solutions    |

#### What is an FPGA

A field-programmable gate array is an integrated circuit designed to be configured by a designer after manufacturing.

Field-Programmable – Means the user can program it in the field

#### **FPGA Architecture**

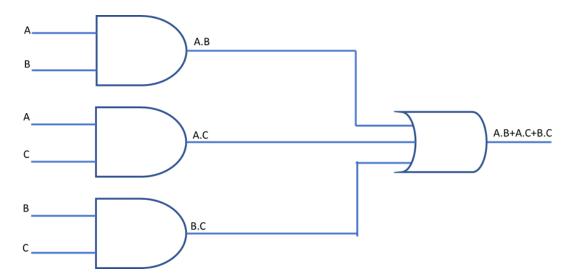

# What is programmable logic

| Input A | Input B | Input C | ОР |

|---------|---------|---------|----|

| 0       | 0       | 0       | 0  |

| 0       | 0       | 1       | 0  |

| 0       | 1       | 0       | 0  |

| 0       | 1       | 1       | 1  |

| 1       | 0       | 0       | 0  |

| 1       | 0       | 1       | 1  |

| 1       | 1       | 0       | 1  |

| 1       | 1       | 1       | 1  |

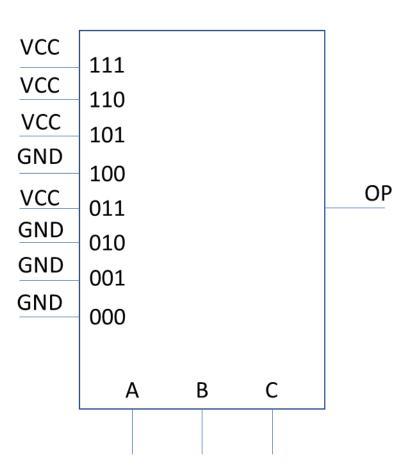

VCC 111 VCC 110 VCC 101 GND 100 VCC 011 GND 010 GND 001 GND 000 В С А

OP

## Look Up Table

- The key to programmable logic is how logic equations are implemented in the device.

- It is of course very difficult for the device designers to include a range of AND, OR gates etc. as the number of each gate type will vary for each application

- Device manufacturers addressed this challenge in a very smart manner. In place of discrete gates, they used they use a several input look up table (LUT) which is programmed to implement the combinatorial logic equations.

## Look Up Table

| Input A | Input B | Input C | ОР |

|---------|---------|---------|----|

| 0       | 0       | 0       | 0  |

| 0       | 0       | 1       | 0  |

| 0       | 1       | 0       | 0  |

| 0       | 1       | 1       | 1  |

| 1       | 0       | 0       | 0  |

| 1       | 0       | 1       | 1  |

| 1       | 1       | 0       | 1  |

| 1       | 1       | 1       | 1  |

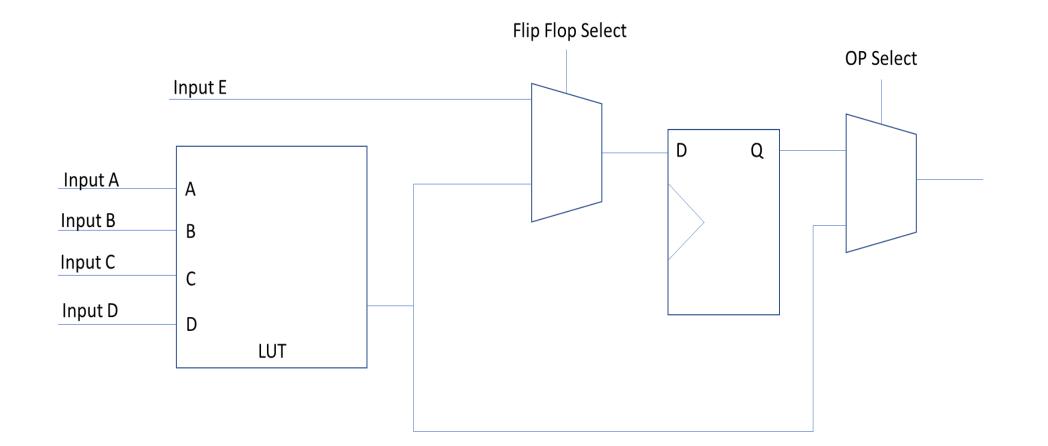

# **Configurable Logic Block**

- LUT allows implementation of Combinatorial Circuit

- BUT we design synchronous circuits what about the FF

- flip flop to act as storage for the combinatorial output such that we can implement sequential structures

- This combination of a LUT and Flip Flop is often called a Configurable Logic Block (CLB) and a programmable logic device will consist of many thousands of these CLBs. To provide the most flexibility additional multiplexers will be used to support a wide range of CLB configurations.

# **Configurable Logic Block**

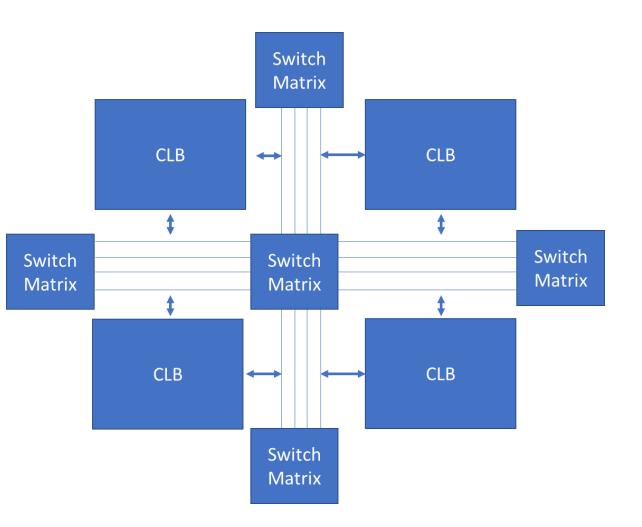

### **Interconnect Routing**

A collection of wires and programmable switches.

These are responsible for connecting CLBs and other building blocks within the FPGA.

These are also called routing channels.

#### Tools

- Requirements Capture tool

- Editors Ideal with ability to LINT and check structural issues e.g HDL Creator

- Synthesis Tool Third Party or Vendor Supplied

- Implementation Vendor supplied some open source for lattice

- Simulation Third Party or Vendor

- Source Control Subversion, GIT

- Configuration control often called PLM tool

- Specialist e.g. Fault Injection

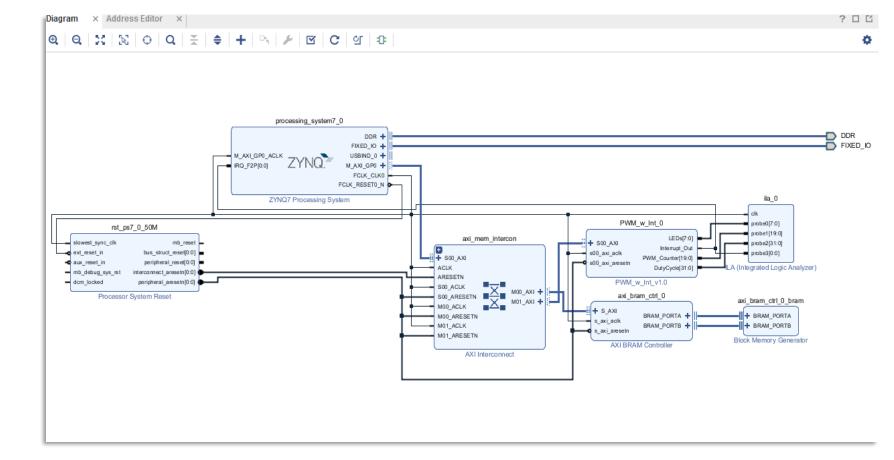

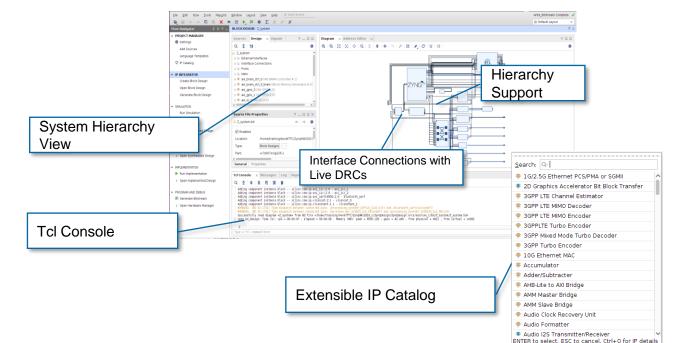

### Vivado Overview

- Foundation of all design and higherlevel tools is Vivado

- Vivado enables us to capture designs using VHDL or Verilog

- Large IP library to accelerate our designs

- Integrates Vivado / Vitis HLS IP cores

#### i

- Simulate designs using Vivado Simulator

- Synthesize, place and route the design

- Generate power estimations

- Create Xilinx Support Architecture

#### Vivado Overview

#### **FPGA Implementation Flow**

**Synthesis** – Translates the HDL design into a series of logic equations which are then mapped onto the resources available in the target FPGA.

**Synthesis** – Place – The logic resources determined by the synthesis tool are placed at available locations within the target device.

**Routing** – The placed logic resources in the design are interconnected using routing and switch matrixes to implement the final application.

Bit File – The generation of the final programming file for the target FPGA.

i

We can control the flow implementation settings by using Constraints (XDC file) and implementation Strategies

# **Xilinx Devices**

# Xilinx Offer a range of devices

FPGA – Spartan, Artix, Kintex, Virtex – Seven / UltraScale / UltraScale+

Heterogeneous SoC – Zynq, Zynq MPSoC, RFSoC

Adaptive Compute Acceleration Platform– Versal

Accelerator Card - Alveo

#### **FPGA**

### Heterogeneous SOC

Combine diverse processing elements with programmable logic

Processing elements are silicon implementations

Processing element is the master – it boots just like any other processor

Enables highly optimized solutions be implemented using processor and logic to exploit natural strengths

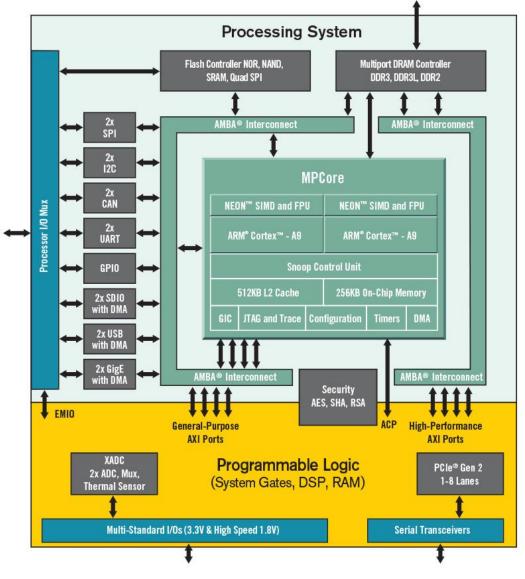

# Zynq

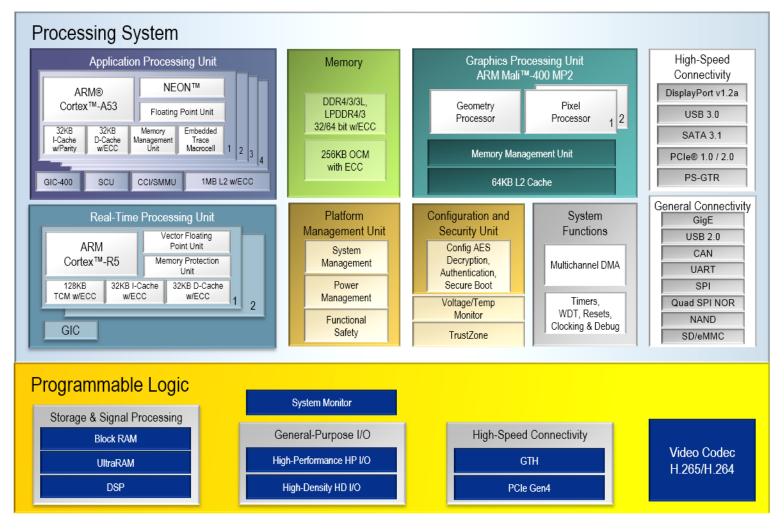

# Zynq MPSoC

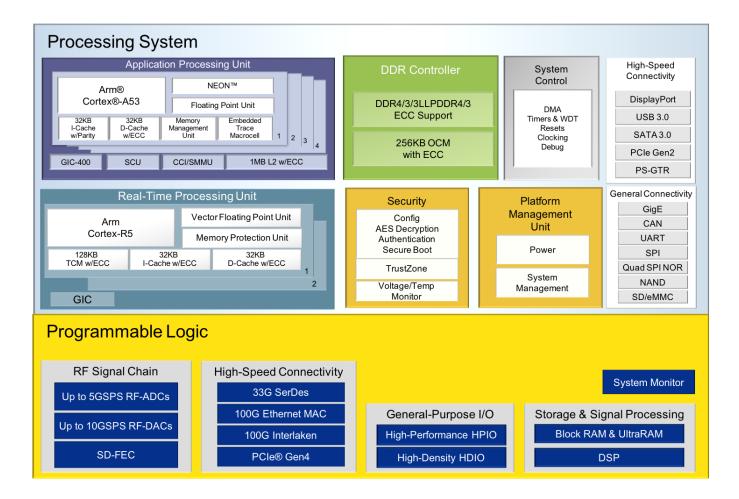

# Zynq RFSoC

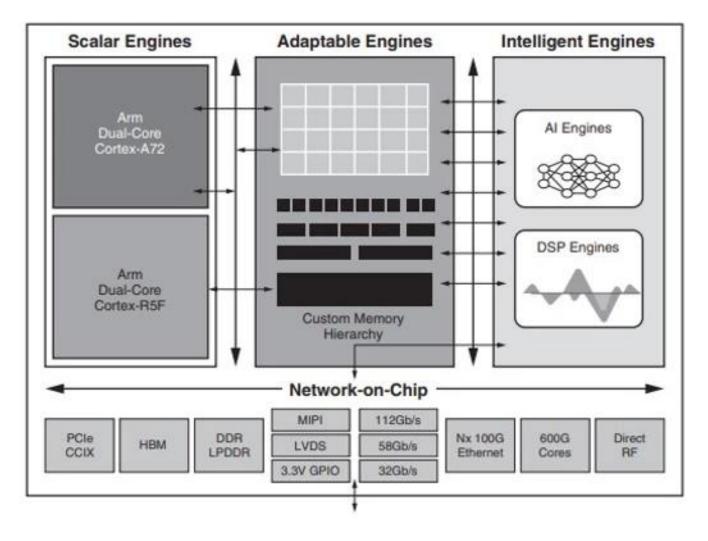

#### Versal

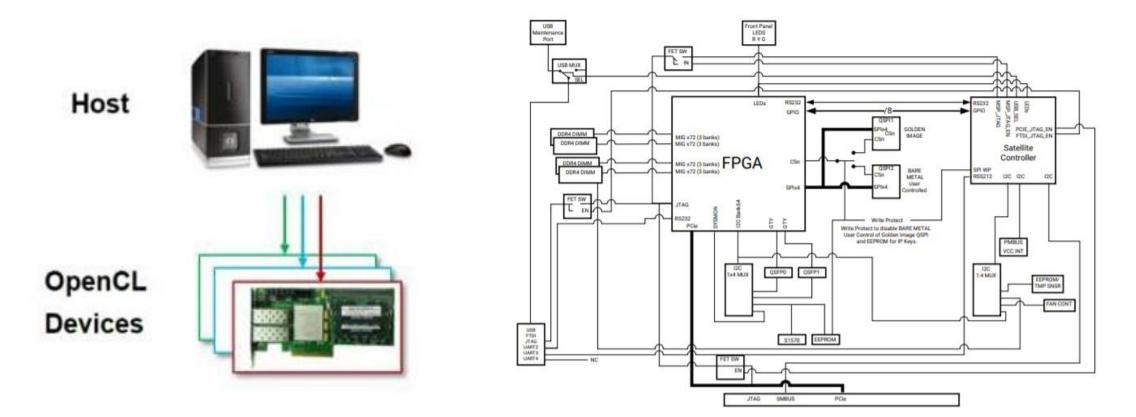

#### **Alveo**

#### Accelerator card based around OpenCL

# Clocking

24

# Clocking

FPGA Designs are Synchronous!

Clocks are high fan out, as such dedicated pins are required to be used.

FPGA typically will have multiple clock regions

Clock pins are places in IO banks

- UltraScale / UltraScale+ GC pins or global clock pins

- Seven Series CC and GC pins GC global clocks CC restricted to close CR

- Special Clock pins e.g. Byte-Lane Clocks (DBC and QBC) typical in memory applications

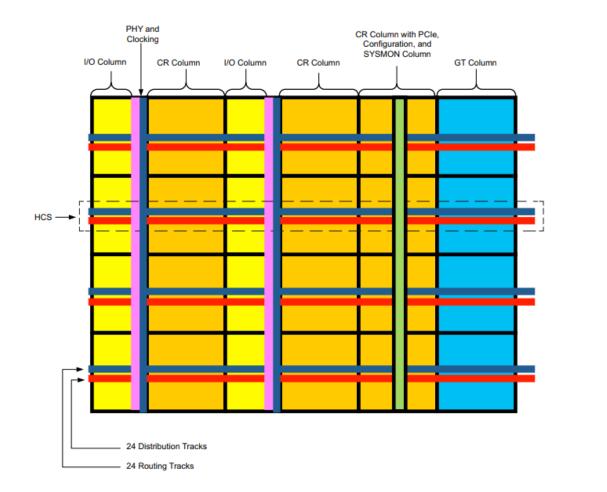

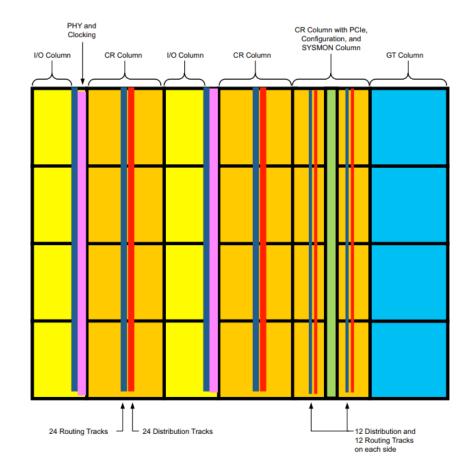

#### **Vertical and Horizontal Clocks**

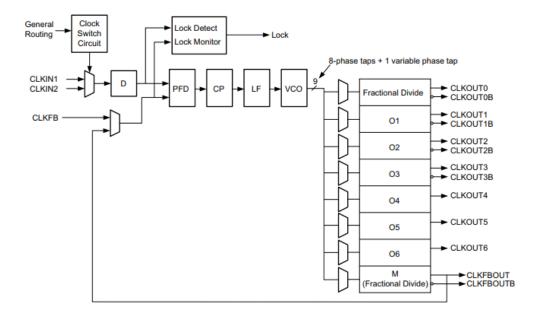

# **Clocking Resources**

FPGA have a range of clock resources to simply solutions

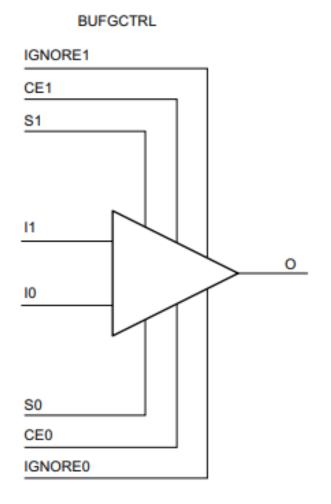

- 1. Clock Buffers e.g. bufgctl

- 2. Clock Management Tiles

- Mixed Mode Clock Manager (MMCM) & 2 Phase Locked Loops

# **Clocking Resources**

Bufgctl - drive the routing and distribution resources across the entire device.

Can switch between 2 clocks seamlessly.

Basis of many structures including

Bufgce\_1, Bufgmux etc.

Read Seven Series, UltraScale clocking guides

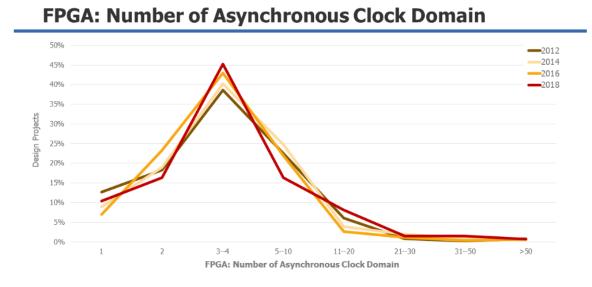

## What is a Clock Domain?

Same clock domain if:

» Same source and integer multiple frequencies

Different clock domain if:

- » Different source

- Even if frequency specification is the same!

- All specifications have error bars

- » Not integer multiple frequencies, even if same source

By default, Vivado assumes all clocks are in the same domain – Unless you tell it otherwise! Not telling it clock relationships can make a significantly longer implementation times as Vivado tries to close timing which is impossible

# **Clock Domain Crossing**

# **Clock Domain Crossing**

Ideal solution uses one clock and the entire design is synchronous.

BUT!

Modern devices have multiple clocks to address different clock domains e.g. ADC / DAC clocks, source synchronous interfaces.

Brings with it the need to transfer data, and signals safely and reliability between the clock domains

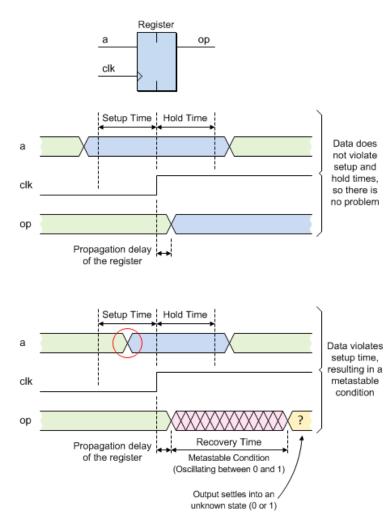

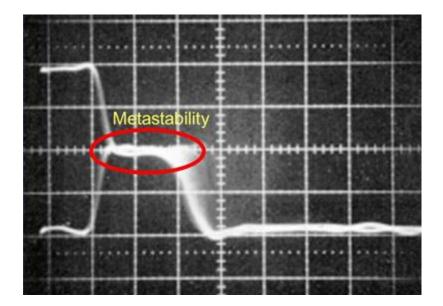

## Metastability

One issue which can arise with incorrect domain crossing is metastability

This can lead to corruption of data or incorrect behaviour

Occurs when a flip flops set up or hold time is violated

### Metastability

# **Clock Domain Crossing**

Several Techniques which can be used depending upon what needs to be transferred

- Two stage synchroniser Ideal for single bit data

- Grey Code Synchroniser Encodes data bus in grey code and transfer between domains – Ideal for counters as input to be converted to grey code can only decrement / increment by one from previous value

- Hand shake synchroniser Transfers data bus between two clock domains using handshake signals

- Pulse synchroniser transfer pulse from one clock domain to another

- Asynchronous FIFO transfers data from one domain to another, useful for high throughput / burst transfers

## **Clock Domain Crossing**

To support reset functionality across clock domains we may need the following synchronisers structures.

- » Asynchronous Reset Synchroniser enables asynchronous assertion and synchronous de-assertion.

- » Synchronous Reset Synchroniser synchronises a synchronous reset to another clock domain.

### How many synchronisers do I need?

Standard two stage synchroniser assumes the first flip flop, will recover from metastability before the signal is clocked into the second flip flop. How do we know this is the case and what if we need more stages

$$MTBF = \frac{e^{t_r/\tau}}{T_o \times f \times a} \times k \left(\frac{e^{t_r/\tau}}{T_o \times f}\right)$$

- $t_r$  = The speed at which the event is being resolved (clock period – setup time)

- T<sub>o</sub> = Time window during which the register is susceptible to going metastable.

- $\tau =$ Settling time

- a = Frequency of the asynchronous signal.

- f = Frequency of the clock (as stated in Part 1, this should be faster than "a")

- k = The number of additional stages (so k=1 for a two-stage synchroniser)

Note that  $\tau$  and T<sub>o</sub> are both process constants.

© Adiuvo Engineering and Training, Ltd. 2020

### **CDC** in Xilinx

Xilinx Parameterised Macros (XPM) – provide CDC structures

Use registers optimised for CDC in the fabric

» Registers located close together and have small set up and hold windows

Described within UG953 Libraries Guide

Described within UG 974 UltraScale Architecture Libraries

| Untitled 1                     |                       |                                          |        |                                      |        |        |          |          |          |          | _ 8 2        |

|--------------------------------|-----------------------|------------------------------------------|--------|--------------------------------------|--------|--------|----------|----------|----------|----------|--------------|

| Q 📕 🔍 Q 🐰                      | •F   I4   M   12   27 | + <b>Г</b>   <b>Г</b> ∉   ⇒ <b>Г</b>   ⊡ |        |                                      |        |        |          |          |          |          |              |

|                                |                       |                                          |        |                                      |        |        |          |          |          |          | 1,965.000 ns |

| Name                           | Value                 |                                          | 200 ns | 400 ns                               | 600 ns | 800 ns | 1,000 ns | 1,200 ns | 1,400 ns | 1,600 ns | 1,800 ns     |

| 🕌 clk_1                        | 1                     |                                          |        | <u>Ta bada da bada da bada da ba</u> |        |        |          |          |          |          |              |

| 🕌 clk_2                        | 0                     |                                          |        |                                      |        |        |          |          |          |          |              |

| 👪 reset                        | 0                     |                                          |        |                                      |        |        |          |          |          |          |              |

| reset_safe                     | 0                     |                                          |        |                                      |        |        |          |          |          |          |              |

| 🕌 start                        | 0                     |                                          |        |                                      |        |        |          |          |          |          |              |

| <pre>&amp; start_retimed</pre> | 0                     |                                          |        |                                      |        |        |          |          |          |          |              |

| > 😼 start_reg[1:0]             | 0                     | x                                        |        | 0                                    |        | 3      |          |          | 0        |          |              |

| > 🕫 counter[15:0]              | 100                   | x                                        |        |                                      |        |        |          |          |          |          | 100          |

| H pulse                        | 1                     | 1                                        |        |                                      |        |        |          |          |          |          |              |

| 🖟 terminal_count               | 100                   |                                          |        |                                      |        | 10     | )        |          |          |          |              |

## **CDC Design Analysis tools**

Detecting all CDC issues can be a challenge in large designs

- » Are all IP IO on the correct clock domain

- » Very easy to associate signal with wrong domain e.g. FIFO empty and WR clock

CDC issues can be very difficult to find changing on each start up and may be intermittent

Can be hard to find in simulation – Timing simulation required, takes a long time simulate the system

Static analysis tools are better suited to find the CDC issues.

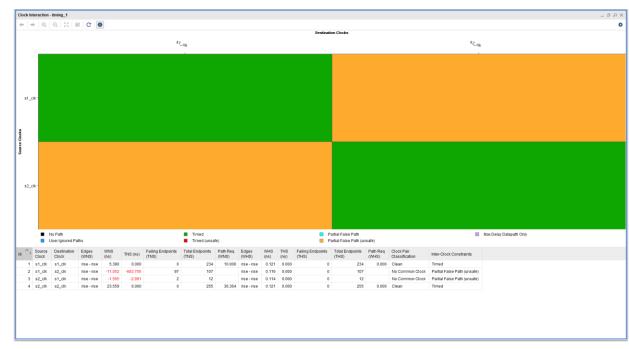

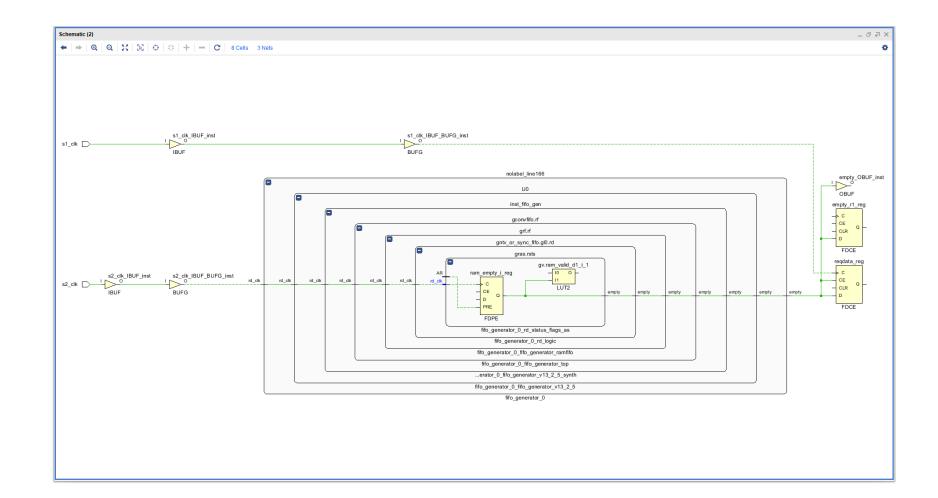

### Vivado CDC Report

Following Synthesis – in TCL window run the command report\_cdc

| onsole                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ? = 1                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| DC Report                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| D Severity Count Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| DC-1 Critical 66 1-bit unknown CDC circuitry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| DC-2 Warning 1 1-bit synchronized with missing ASYNC_REG property<br>DC-3 Info 2 1-bit synchronized with ASYNC REG property                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| DC-9 Info 2 Asynchronous reset synchronized with ASYNC_REG property<br>DC-15 Warning 32 Clock enable controlled CDC structure detected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ource Clock: input port clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| stination Clock: sl_clk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| DC Type: No Common Primary Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Exception Source (From) Destination (To)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1 CDC-9 Info Asynchronous reset synchronized with ASYNC_REG property 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | False Path reset_n UF/U0/inst_fifo_gen/gconvfifo.rf/grf.rf/rstblk/ngwrdrst.grst.g7serrst.gnsckt_wrst.rs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | t_wr_reg2_inst/arststages_ff_reg[0]/PRE                                                                                                                                                                                                                                                                                                                                                                                                |

| ource Clock: s2_clk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| estination Clock: sl_clk<br>DC Type: No Common Primary Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Destination (To)                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ow ID Severity Description Depth Exception                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Source (From)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Descinación (10)                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1 CDC-3 Info 1-bit synchronized with ASYNC_REG property 5 False Path 1<br>2 CDC-1 Critical 1-bit unknown CDC circuity 0 None 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | UF/U0/inst_fifo_gen/gconvfifo.rf/grf.rf/rstblk/ngwrdrst.grst.g79errst.gnsckt_wrst.gic_rst.sckt_rd_rst_ic_reg/C<br>UE/U0/inst_fifo_gen/gconvfifo.rf/grf.rf/gntv_or_sync_fifo.gl0.rd/gras.rsts/ram_empty_i_reg/C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | JF/U0/inst_fifo_gen/gconvfifo.rf/grf.rf/rstblk/ngwrdrst.grst.g7<br>reqdata_reg/CE                                                                                                                                                                                                                                                                                                                                                      |

| 1 CDC-3 Info 1-bit synchronized with ASYNC_REG property 5 False Path 1<br>2 CDC-1 Critical 1-bit unknown CDC circuity 0 None 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | UF/V0/inst_fifo_gen/gconvfifo.rf/grf.rf/rstblk/ngwrdrst.grst.grserrst.gnsckt_wrst.gic_rst.sckt_rd_rst_ic_reg/C<br>UF/V0/inst_fifo_gen/gconvfifo.rf/grf.rf/gntv_or_sync_fifo.q10.rd/gras.rsts/ram_empty_i_reg/C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | JF/U0/inst_fifo_gen/gconvfifo.rf/grf.rf/rstblk/ngwrdrst.grst.g7                                                                                                                                                                                                                                                                                                                                                                        |

| 1 CDC-3 Info 1-bit synchronized with ASYNC_REG property 5 False Path 1     2 CDC-1 Critical 1-bit unknown CDC circuitry 0 None 1     3 CDC-1 Critical 1-bit unknown CDC circuitry 0 None 1     ource Clock: input port clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | UF/U0/inst_fifo_gen/gconvfifo.rf/grf.rf/rstblk/ngwrdrst.grst.g79errst.gnsckt_wrst.gic_rst.sckt_rd_rst_ic_reg/C<br>UE/U0/inst_fifo_gen/gconvfifo.rf/grf.rf/gntv_or_sync_fifo.gl0.rd/gras.rsts/ram_empty_i_reg/C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | JF/U0/inst_fifo_gen/gconvfifo.rf/grf.rf/rstblk/ngwrdrst.grst.g7<br>reqdata_reg/CE                                                                                                                                                                                                                                                                                                                                                      |

| 1 CDC-3         Info         1-bit synchronized with ASYNC_REG property         5         False Path           2 CDC-1         Critical         1-bit unknown CDC circuitry         0         None         1           3 CDC-1         Critical         1-bit unknown CDC circuitry         0         None         1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | UF/U0/inst_fifo_gen/gconvfifo.rf/grf.rf/rstblk/ngwrdrst.grst.g79errst.gnsckt_wrst.gic_rst.sckt_rd_rst_ic_reg/C<br>UE/U0/inst_fifo_gen/gconvfifo.rf/grf.rf/gntv_or_sync_fifo.gl0.rd/gras.rsts/ram_empty_i_reg/C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | JF/U0/inst_fifo_gen/gconvfifo.rf/grf.rf/rstblk/ngwrdrst.grst.g7<br>reqdata_reg/CE                                                                                                                                                                                                                                                                                                                                                      |

| 1 CDC-3 Info 1-bit synchronised with ASYNC_REG property 5 False Path 1     2 CDC-1 Critical 1-bit unknown CDC circuitry 0 None 1     3 CDC-1 Critical 1-bit unknown CDC circuitry 0 None 1     ource Clock: input port clock     evination toost 32 circ DC Type: No Common Primary Clock     ow ID Severity Description Depth                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | UF/U0/inst_fifo_gen/gconvfifo.rf/grf.rf/rstblk/ngwrdrst.grst.grserrst.gnsckt_wrst.gic_rst.sckt_rd_rst_io_reg/C<br>UE/U0/inst_fifo_gen/gconvfifo.rf/grf.rf/gntv_or_sync_fifo.gl0.rd/gras.rsts/ram_empty_i_reg/C<br>UF/U0/inst_fifo_gen/gconvfifo.rf/grf.rf/gntv_or_sync_fifo.gl0.rd/gras.rsts/ram_empty_i_reg/C<br>Exception Source (From) Destination (To)                                                                                                                                                                                                                                                                                                                                                                                                     | UF/U0/inst_fifo_gen/goonvfifo.rf/grf.rf/rstblk/ngwrdrst.grst.g7<br>cegdata_reg/CE<br>cegdata_reg/D                                                                                                                                                                                                                                                                                                                                     |

| 1 CDC-3 Info 1-bit synchronised with ASYNC_REG property 5 False Path 1     2 CDC-1 Critical 1-bit unknown CDC circuitry 0 None 1     3 CDC-1 Critical 1-bit unknown CDC circuitry 0 None 1     ource Clock: input port clock     evination toost 32 circ DC Type: No Common Primary Clock     ow ID Severity Description Depth                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | UF/U0/inst_fifo_gen/gconvfifo.rf/grf.rf/rstblk/ngwrdrst.grst.g79errst.gnsckt_wrst.gic_rst.sckt_rd_rst_ic_reg/C<br>UE/U0/inst_fifo_gen/gconvfifo.rf/grf.rf/gntv_or_sync_fifo.gl0.rd/gras.rsts/ram_empty_i_reg/C<br>UF/U0/inst_fifo_gen/gconvfifo.rf/grf.rf/gntv_or_sync_fifo.gl0.rd/gras.rsts/ram_empty_i_reg/C<br>ExceptionSource (From)_Destination (To)                                                                                                                                                                                                                                                                                                                                                                                                      | DF/U0/inst_fifo_gen/goonvfifo.rf/grf.rf/rstblk/ngwrdrst.grst.g7<br>regdata_reg/CE<br>regdata_reg/D                                                                                                                                                                                                                                                                                                                                     |

| 1     CDC-3     Info     1-bit synchronized with ASYNC_REG property     5     False Path       2     CDC-1     Critical     1-bit unknown CDC circuitry     0     None     1       3     CDC-1     Critical     1-bit unknown CDC circuitry     0     None     1       ource     Clock:     input port clock     0     None     1       D'Type: NC Common Frimary Clock     0     Depth     1     Depth       1     CDC-9     Info     Asynchronous reset synchronized with ASYNC_REG property     2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | UF/U0/inst_fifo_gen/goonvfifo.rf/grf.rf/rstblk/ngwrdrst.grst.g7serrst.gnsckt_wrst.gio_rst.sckt_rd_rst_io_reg/C<br>UE/U0/inst_fifo_gen/goonvfifo.rf/grf.rf/gntv_or_sync_fifo.gl0.rd/gras.rsts/ram_empty_i_reg/C<br>UF/U0/inst_fifo_gen/goonvfifo.rf/grf.rf/gntv_or_sync_fifo.gl0.rd/gras.rsts/ram_empty_i_reg/C<br>Exception Source (From) Destination (To)                                                                                                                                                                                                                                                                                                                                                                                                     | DF/U0/inst_fifo_gen/goonvfifo.rf/grf.rf/rstblk/ngwrdrst.grst.g7<br>regdata_reg/CE<br>regdata_reg/D                                                                                                                                                                                                                                                                                                                                     |

| 1 CDC-3 Info 1-bit synchronized with ASYNC_REG property 5 False Path 1     2 CDC-1 Critical 1-bit unknown CDC circuitry 0 None 1     3 CDC-1 Critical 1-bit unknown CDC circuitry 0 None 1     ource Clock: input port clock     setination croox: s2_clx     Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | UF/U0/inst_fifo_gen/goonvfifo.rf/grf.rf/rstblk/ngwrdrst.grst.g7serrst.gnsckt_wrst.gio_rst.sckt_rd_rst_io_reg/C<br>UE/U0/inst_fifo_gen/goonvfifo.rf/grf.rf/gntv_or_sync_fifo.gl0.rd/gras.rsts/ram_empty_i_reg/C<br>UF/U0/inst_fifo_gen/goonvfifo.rf/grf.rf/gntv_or_sync_fifo.gl0.rd/gras.rsts/ram_empty_i_reg/C<br>Exception Source (From) Destination (To)                                                                                                                                                                                                                                                                                                                                                                                                     | DF/U0/inst_fifo_gen/goonvfifo.rf/grf.rf/rstblk/ngwrdrst.grst.g7<br>regdata_reg/CE<br>regdata_reg/D                                                                                                                                                                                                                                                                                                                                     |

| 1 CDC-3 Info 1-bit synchronized with ASYNC_REG property 5 False Path 1<br>2 CDC-1 Critical 1-bit unknown CDC circuitry 0 None 1<br>3 CDC-1 Critical 1-bit unknown CDC circuitry 0 None 1<br>ource Clock: input port clock<br>Setimation Clock # 2 fix<br>DC Type: No Common Primary Clock<br>ow ID Severity Description Depth<br>1 CDC-9 Info Asynchronous reset synchronized with ASYNC_REG property 2<br>ource Clock: s1_clk<br>estimation Clock: s2_clk<br>DC Type: No Common Primary Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | UF/U0/inst_fifo_gen/gconvfifo.rf/grf.rf/rstblk/ngwrdrst.grst.grserrst.gnsckt_wrst.gic_rst.sckt_rd_rst_io_reg/C<br>UE/U0/inst_fifo_gen/gconvfifo.rf/grf.rf/gntv_or_sync_fifo.gl0.rd/gras.rsts/ram_empty_i_reg/C<br>UF/U0/inst_fifo_gen/gconvfifo.rf/grf.rf/gntv_or_sync_fifo.gl0.rd/gras.rsts/ram_empty_i_reg/C<br>Exception Source (From) Destination (To)<br>                                                                                                                                                                                                                                                                                                                                                                                                 | UF/U0/inst_fifo_gen/geonvfifo.rf/grf.rf/rstblk/ngwrdrst.grst.g7<br>cegdata_reg//E<br>cegdata_reg/D<br>                                                                                                                                                                                                                                                                                                                                 |