Table of Contents

Zmod Digitizer Reference Manual

The Digilent Zmod Digitizer is a SYZYGY™ 1)compatible pod containing a dual-channel ADC and the associated front end. The Zmod Digitizer is intended to be used with any SYZYGY™ compatible carrier board having the required capabilities.

Features

Table 1. Zmod Digitizer family features

| Features/Version | 1430-125 |

|---|---|

| ADC | AD9648BCPZ-125 |

| Input Channels | 2 |

| Input Range | ±1 V |

| Resolution [bits] | 14 bits |

| Absolute Resolution | 0.13 mV |

| Accuracy [% of Input Range] 1) | ±0.5% |

| Sample Rate - Max [MS/s] | 125 MS/s |

| Analog Bandwidth @ 3 dB | 60 MHz |

| Analog Bandwidth @ 0.5 dB | 20 MHz |

| Analog Bandwidth @ 0.1 dB | 8 MHz |

| Input Impedance [MΩ] | 1 MΩ || 5 pF |

1. Architectural Overview and Block Diagram

This document describes the Zmod Digitizer's circuits, with the intent of providing a better understanding of its electrical functions, operations, and a more detailed description of the hardware’s features and limitations. It is not intended to provide enough information to enable complete duplication of the Zmod Digitizer, but can help users to design custom configurations for programmable parts in the design.

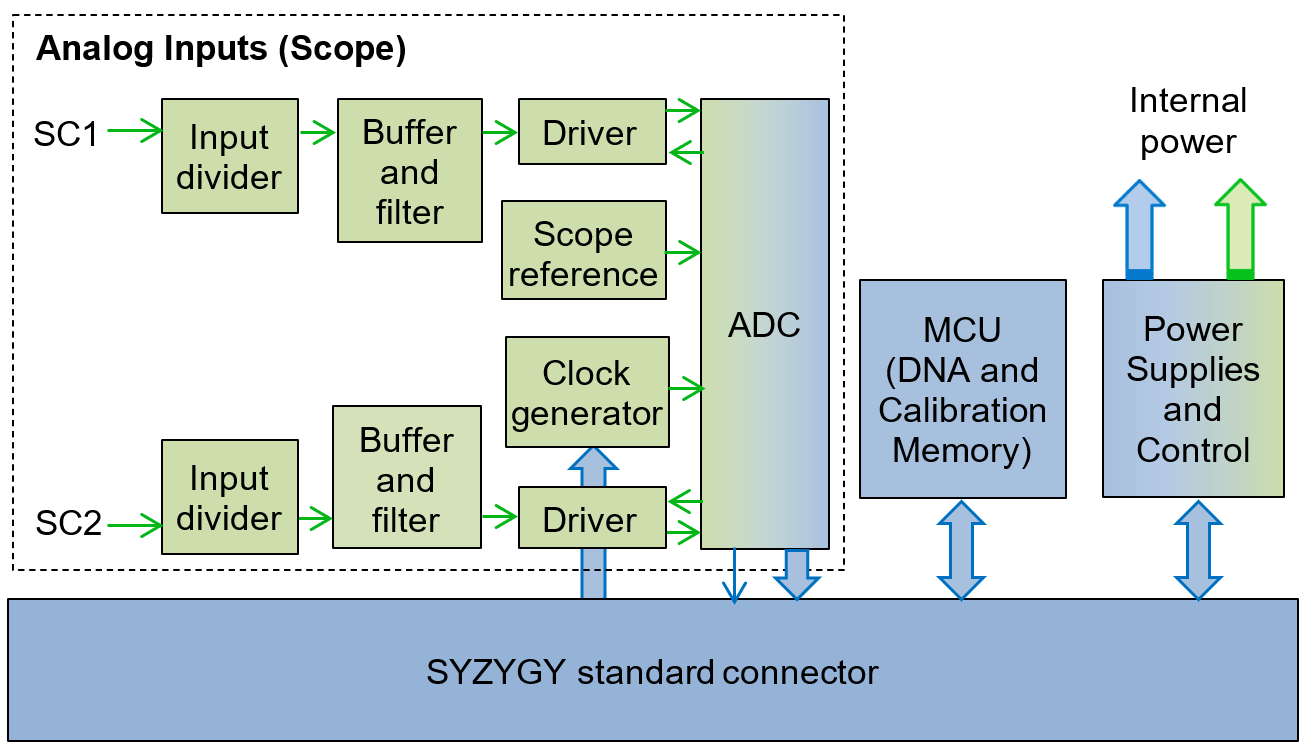

Zmod Digitizer's block diagram is presented in Fig. 1 below. The core of the Analog Zmod Digitizer is a dual channel, high speed, low power ADC, as shown in Table 1. The carrier board is responsible to configure the internal registers of the ADC and clock generator circuits, and receive the data.

The Analog Input block has a similar structure and behavior to a scope frontend, for that reason some of the signals in this circuitry use the “SC” index to indicate that they are related to the scope block. Signals and equations also use certain naming conventions. Analog voltages are prefixed with a “V” (for voltage), and suffixes and indexes are used in various ways: to specify the location in the signal path (IN, BUF, ADC, etc.); to indicate the related instrument (SC, etc.); to indicate the channel (1 or 2); and to indicate the type of signal (P, N, or diff). Referring to the block diagram in Fig. 1 below:

- The Analog Input (Scope) instrument block includes:

- Input Divider: high bandwidth input adapter/divider.

- Buffer and filter: high impedance buffer and anti-alias filter

- Driver: provides appropriate signal levels and protection to the ADC.

- Scope Reference: generates and buffers reference voltages for the scope stages

- Clock Generator: generates a low jitter, programmable frequency clock for data acquisition

- ADC: the analog-to-digital converter for both digitizer channels.

- The Power Supplies and Control block generates all internal supply voltages.

- The MCU works as an I2C memory for two different purposes:

- The DNA includes the standard SYZYGY™ pod identification information.

- The Calibration Memory stores all calibration parameters. Except for the “Probe Calibration” trimmers in the Input Divider, the Zmod Digitizer includes no analog calibration circuitry. Instead, a calibration operation is performed at manufacturing (or by the user), and parameters are stored in memory. The application software uses these parameters to correct the acquired data.

In the sections that follow, schematics are not shown separately for identical blocks. For example, the Input Divider schematic is only shown for channel 1 since the schematic for channel 2 is identical. Indexes are omitted where not relevant. As an example, in equation \ref{1} below, $V_{SCOPE-SMA}$ does not contain the channel index (because the equation applies to both channels 1 and 2).

Figure 1. Zmod Digitizer Block diagram.

2. Analog Input

2.1. Input Divider

C2, C3, C4, R3, R5 and R6 build a frequency compensated input divider. C4 is a capacitive trimmer, 5…20 pF, -0/+50% tolerance. The worse case range is 7.5…20 pF. All other capacitors are 1% tolerance, all the resistors are 0.1%.

The input divider provides:

- Analog input impedance = 1 MOhm || 5 pF

- a 0.25 attenuation

- Controlled capacitance, much higher than the parasitical capacitance of subsequent stages

- Constant attenuation over a large frequency range (trimmer adjusted)

The maximum voltage rating for analog inputs is limited to:

$$-50V<V_{SCOPE1-SMA}<50V\label{1}\tag{1}$$

The DC gain is: $$\frac {V_{DIV1}}{V_{SCOPE1-SMA}}=\frac {R_5 + R_6}{R_3+R_5 + R_6}=0.25\label{2}\tag{2}$$

The nominal input voltage range is: $$-1V \le V_{SCOPE1-SMA} \le 1V \label{3}\tag{3}$$

The divider equivalent impedance is:

$$R_{ech} = R_3 + R_5 + R_6 = 1Mohm\label{4}\tag{4}$$

Experiments shown that there is significant parasitic capacity in the VDIV1 node: CP includes the capacity to GND of the layout, buffer input stage and protection diode D1 and is parallel to (C3, C4). The trimmer should compensate for these parasitic capacities and adjust for perfect matching:

$$C_2*R_3 = (\frac{C_3*C_4}{C_3+C_4} + C_P)*(R_5+R_6)\label{5}\tag{5}$$

The equivalent capacitance of the input divider (SCOPE1_SMA node) is:

$$C_{ech} = 5.1pF\label{6}\tag{6}$$

2.2. Buffer and Filter

The buffer stage provides very high impedance as load for the input divider. The buffer has no internal input protection diode, so D1 was added. The anti-alias filter has a bandwidth of 60MHz.

2.3. Driver

The ADC driver is used for:

- Driving the differential inputs of the ADC (with low impedance outputs)

- Providing the common mode voltage for the ADC

- ADC protection.

The total gain of the buffer, amplifier and driver is:

$$\frac {V_{ADC\;diff}}{V_{DIV1}}=3.8\label{7}\tag{7}$$

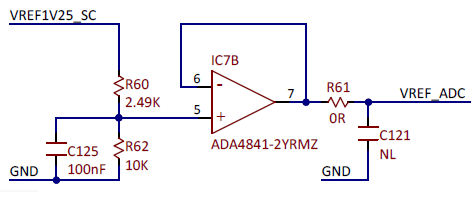

2.4. Scope Reference

The scope reference stage generates the 1.25 V reference voltage which is decreased to 1 V, buffered by IC7B and provided to the ADC.

2.5. ADC

The Zmod Digitizer uses a dual channel, high speed, low power, 14-bit, 125 MS/s ADC, as shown in Fig. 4.

Figure 4. ADC

The differential inputs are impedance matched with the driver stage.

The differential clock is AC-coupled and the line is impedance matched. The ADC generates the common mode reference voltage (VCM_SC) to be used in the buffer stage.

The digital stage of the ADC and the corresponding FPGA bank are supplied at 1.8 V by the SYZYGY™ voltage Vadj.

The multiplexed mode is used, to combine the two channels on a single data bus and minimize the number of used FPGA pins. CLKOUT_SC is provided to the FPGA for synchronizing data.

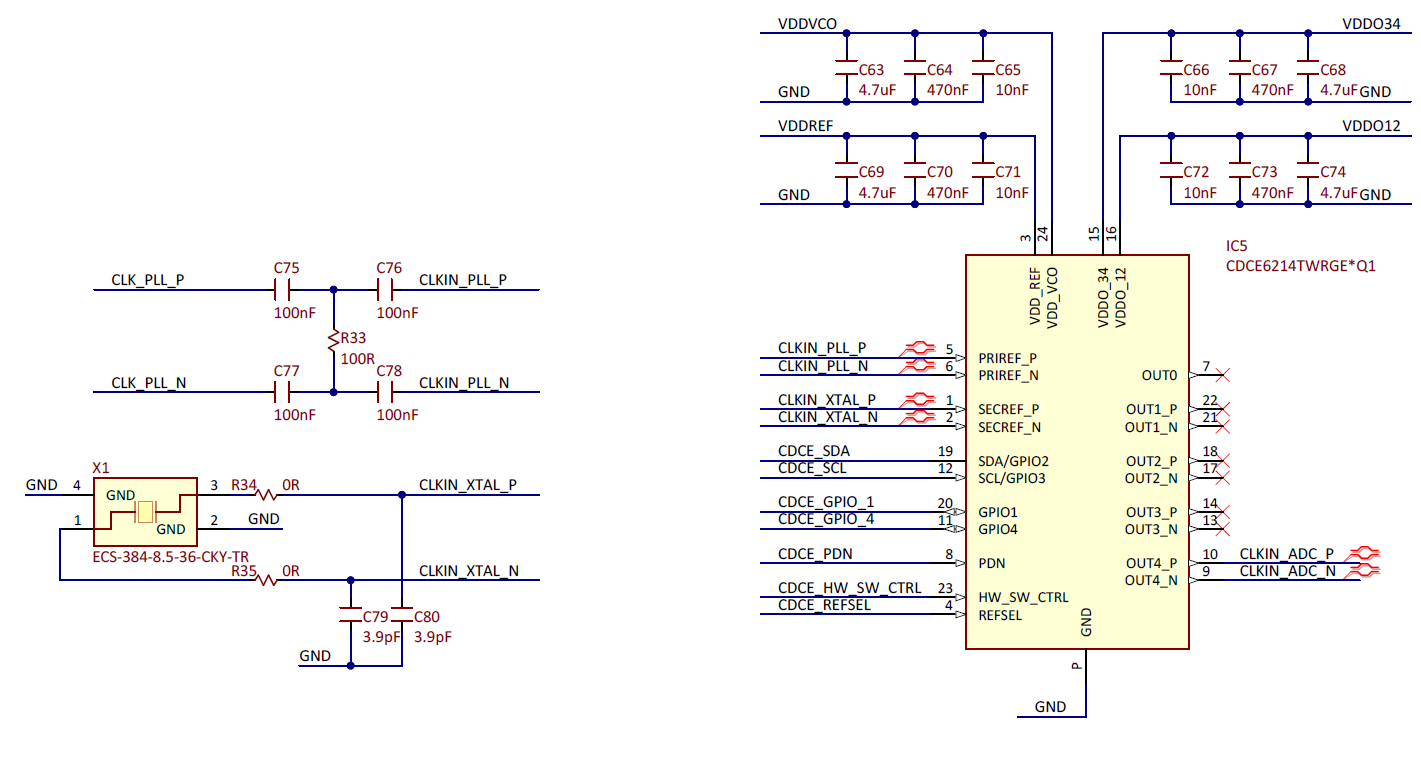

2.6. Clock Generator

IC5 in the figure below is a low jitter clock generator: CDCE6214. It has a PLL loop, with divider and multiplier registers, for programmable output frequencies. An input MUX can select between two possible clock sources:

- Zmod Digitizer uses a crystal for a low jitter clock source at CLKIN_XTAL pins.

- As an alternative, the SYZYGY C2P clock can be selected at CLKIN_PLL pins, for a flexible, lower-quality clock source, originating at the carrier board FPGA.

OUT4 pins generate the LVDS clock for the ADC, CLKIN_ADC.

The circuit is programmed via a dedicated I2C bus, which is not the standard SYZYGY I2C bus used to communicate with the ADN MCU of the Zmod.

Figure 5. Clock Generator

2.7 Signal Scaling

The nominal differential ADC input voltage range is:

$$-1V<V_{ADC\;diff}<1V\label{8}\tag{8}$$

The total analog gain (from the SMA connectors to the ADC inputs) is:

$$Analog\; gain = \frac{V_{ADC\;diff}}{V_{SCOPE-SMA}}=0.948\label{9}\tag{9}$$

Considering the ADC input voltage range shown in \ref{8}:

$$ -1.055V<V_{SCOPE-SMA}<1.055V=Range\label{10}\tag{10}$$

To cover component value tolerances and to allow software calibration, only the range below is specified.

$$ -1V<V_{SCOPE-SMA}<1V\label{11}\tag{11}$$

With the 14-bit ADC, the absolute resolution is (see Table 1):

$$ \frac{2.11V}{2^{n}}=0.13mV\label{12}\tag{12}$$

For Vin voltage value at the input of the analog channel, the Zmod Digitizer sends a signed n bit integer, N. This value is used to compute Vin:

$$V_{in} = \frac{N \cdot Range \cdot (1+CG)}{2^{n-1}} + CA \label{13}\tag{13}$$

were:

- n = 14, the number of bits of the ADC

- Vin= the corrected value of the input voltage

- N = the n bit, 2's complement integer number returned by the ADC

- Range = 1.055 V = the ideal Range of the input stage (approximation of the values in equation \ref{9}):

- CA = calibration Additive constant (for the appropriate channel and frequency; see paragraph 2.8 and Table 4)

- CG = calibration Gain constant (for the appropriate channel and frequency; see paragraph 2.8 and Table 4)

2.8 Sampling Frequency Characteristics

The S&H capacitance at the input of the ADC, together with the PCB inductance form a resonant circuitry excited by the sampling frequency. In terms of ADC numerical results, this generates gain and offset errors which are dependent on the Sampling frequency. To minimize the effect, two solutions are implemented:

- R10 and R13 values were chosen to optimally damp the oscillation at the ADC differential input.

- The calibration constants are computed and stored in the DNA MCU for 7 different sampling frequencies (122.88 MHz, 50 MHz, 80 MHz, 100 MHz, 110 MHz, 120 MHz, and 125 MHz). For applications requiring high accuracy, the appropriate set of calibration constants should be used, as explained in the Signal Scaling paragraph. For less sensitive applications, the user can choose to use the same set of calibration constants for whatever sampling frequency.

The figure below shows typical errors for the two cases.

- The input voltage for both channels is set to a DC value of -0.9 V (left), 0 V, (middle) and 0.9 V (right)

- Multiple acquisitions are performed at sampling frequencies between 50 MHz and 125 MHz.The absolute error between the measured value and ideal input voltage is displayed as a function of sampling frequency.

- The graphs in the upper row use the set of constants that were computed at a sampling frequency of 122.88 MHz.

- The graphs in the lower row interpolate the 7 sets of constants when browsing the actual sampling frequency.

2.9 Analog Spectral Characteristics

Fig. 7 shows a typical spectral characteristic of the analog input stage. A PXIe-5433 80 MHz Function/Arbitrary Waveform Generator was used to generate the input sinus signal of 0.9 V. A Tektronix DPO5204B scope was used for measuring the reference signal (at the scope SMA connector) and the output signal (at the input of the ADC). A differential probe was used to read the output signal on the pads of the unloaded C118. The signal swept from 800 kHz to 80 MHz. The effective values of the input and output signals were recorded for each frequency. The measurements were further processed to display the input stage frequency characteristics, as shown in Fig. 7.

The 3 dB bandwidth is 60+ MHz. The 0.5 dB bandwidth is 20 MHz and the 0.1 dB bandwidth is 8 MHz.

The standard -3dB bandwidth definition is derived from filter theory. At cutout frequency, the scope attenuates the spectral components by 0.707, assuming an error of ~30%, way too high for a measuring instrument. The bandwidth with a specified flatness is useful to better define the scope spectral performances. The bandwidth @ 0.5 dB, means a flatness error of a max 5.6%, while bandwidth @ 0.1 dB means flatness error of a max 1.1%.

Figure 7. Input stage Bandwidth, 0.5 dB detail (right)

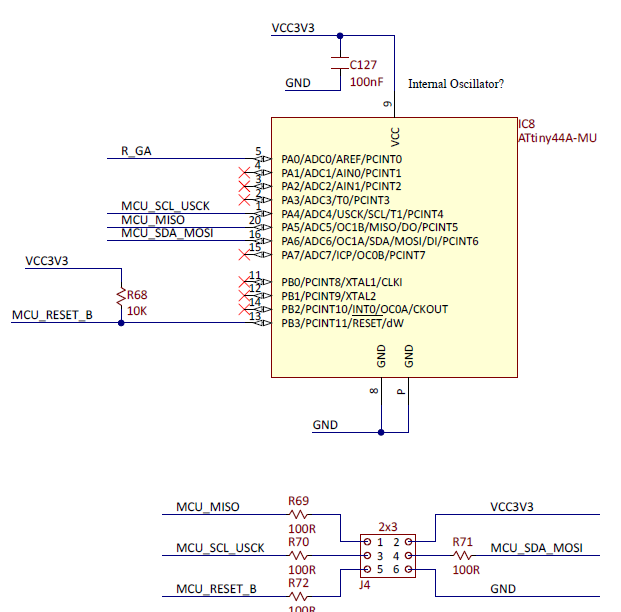

3. MCU

The ATtinny44 MCU in Fig. 8 works as a I2C memory, storing the SYZYGY™ DNA information and the Calibration Coefficients. The J4 connector is used for programming the MCU and the SYZYGY™ DNA at manufacturing.

The DNA and the Factory Calibration Coefficients are stored in the Flash memory of the MCU, which appears to the I2C interface as “read-only”. The User Calibration Coefficients are stored in the EEPROM memory of the MCU, which is write-protected via a magic number at a magic address. The memory structure can be consulted below.

Figure 8. The MCU

- Program Memory Type: Flash

- Program Memory Size (KB): 4

- CPU Speed (MIPS/DMIPS): 20

- SRAM Bytes: 256

- Data EEPROM/HEF (bytes): 256

- Digital Communication Peripherals: 1-SPI, 1-I2C

- Capture/Compare/PWM Peripherals: 1 Input Capture, 1 CCP, 4PWM

- Timers: 1 x 8-bit, 1 x 16-bit

- Number of Comparators: 1

- Temperature Range (C): -40 to 85

- Operating Voltage Range (V): 1.8 to 5.5

- Pin Count: 14

- Low Power: Yes

Table 2. The Flash memory structure

| Address | Function | Size (Bytes) |

|---|---|---|

| 0x8000 - 0x80FF | DNA | 256 |

| 0x8100 - 0x817F | Factory Calibration | 128 |

| 0x8180 - 0x83FF | Future use | 896 |

3.1. SYZYGY™ DNA

The Zmod Digitizer is compliant with SYZYGY™ Specification. It contains an MCU able to calculate the Geographical Address and provide the DNA information via I2C. The DNA is stored in the MCU FLASH at the address range: 0x8000 - 0x80FF with the following structure:

Table 3. The Zmod Digitizer DNA structure

| Contents | Type | Size(Bytes) | Value | Address |

|---|---|---|---|---|

| DNA full data length | uint16 | 2 | 91 | 0x8000 |

| DNA header length | uint16 | 2 | 40 | 0x8002 |

| SYZYGY DNA major version | uint8 | 1 | 1 | 0x8004 |

| SYZYGY DNA minor version | uint8 | 1 | 0 | 0x8005 |

| Required SYZYGY DNA major version | uint8 | 1 | 0 | 0x8006 |

| Required SYZYGY DNA minor version | uint8 | 1 | 0 | 0x8007 |

| Maximum operating 5V load (mA) | uint16 | 2 | 400 | 0x8008 |

| Maximum operating 3.3V load (mA) | uint16 | 2 | 100 | 0x800A |

| Maximum VIO load (mA) | uint16 | 2 | 270 | 0x800C |

| Attribute flags | uint16 | 2 | 0 | 0x800E |

| Minimum operating VIO (10 mV steps) | uint16 | 2 | 180 | 0x8010 |

| Maximum operating VIO (10 mV steps) | uint16 | 2 | 180 | 0x8012 |

| Minimum operating VIO (10 mV steps) | uint16 | 2 | 170 | 0x8014 |

| Maximum operating VIO (10 mV steps) | uint16 | 2 | 190 | 0x8016 |

| Minimum operating VIO (10 mV steps) | uint16 | 2 | 0 | 0x8018 |

| Maximum operating VIO (10 mV steps) | uint16 | 2 | 0 | 0x801A |

| Minimum operating VIO (10 mV steps) | uint16 | 2 | 0 | 0x801C |

| Maximum operating VIO (10 mV steps) | uint16 | 2 | 0 | 0x801E |

| Manufacturer name length | uint8 | 1 | 12 | 0x8020 |

| Product name length | uint8 | 1 | 23 | 0x8021 |

| Product model / Part number length | uint8 | 1 | 23 | 0x8022 |

| Product version / revision length | uint8 | 1 | 1 | 0x8023 |

| Serial number length | uint8 | 1 | 12 | 0x8024 |

| RESERVED | uint8 | 1 | 0 | 0x8025 |

| CRC-16 (most significant byte) | uint8 | 1 | CRC computed over the addresses 0x8000-0x8025: most significant byte | 0x8026 |

| CRC-16 (least significant byte) | uint8 | 1 | CRC computed over the addresses 0x8000-0x8025: least significant byte | 0x8027 |

| END DATA HEADER | ||||

| Manufacturer name | string | 12 | Digilent Inc | 0x8028 |

| Product name | string | 23 | Zmod Digitizer 1430-125 | 0x8034 |

| Product model / Part number | string | 23 | Zmod Digitizer 1430-125 | 0x804B |

| Product version / revision | string | 1 | A, B, C, etc - upon case | 0x8062 |

| Serial number | string | 12 | ??????000000 | 0x8063 |

| Product ID | uint32 | 4 | 0x80406100 | 0x80FC |

3.2. Calibration Memory

The analog circuitry described in previous chapters includes passive and active electronic components. The datasheet specs show parameters (resistance, capacitance, offsets, bias currents, etc.) as typical values and tolerances. The equations in previous chapters consider typical values. Component tolerances affect DC and AC performances of the Zmod Digitizer. To minimize these effects, the design uses:

- 0.1% resistors and 1% capacitors in all the critical analog signal paths

- Capacitive trimmers for balancing the Input Divider and Gain Selection

- No other mechanical trimmers (as these are big, expensive, unreliable and affected by vibrations, aging, and temperature drifts)

- Software calibration, at manufacturing

- User software calibration, as an option

Software calibration is performed on each device as a part of the manufacturing test. Reference signals are connected to the inputs. A set of measurements is used to identify all the DC errors (Gain, Offset) of each analog stage. Correction (Calibration) parameters are computed and stored in the Calibration Memory, on the Zmod Digitizer device, both as Factory Calibration Data and User Calibration Data. The WaveForms software allows the user to perform in-house calibration and overwrite the User Calibration Data. Returning to Factory Calibration is always possible.

The Software reads the calibration parameters from the Zmod Digitizer MCU via the I2C bus and uses them to correct the acquired signals. The structure of the calibration data is shown below:

Table 4. The Calibration Data Structure

| Heading 1 | Name | Size (Bytes) | Type | Flash Address (Factory Calibration) | EEPROM Address (User Calibration) |

|---|---|---|---|---|---|

| Magic ID | 1 | uchar: 0xDD | 0x8100 | 0x7000 | |

| Calibration Time | 4 | unix timestamp | 0x8101 | 0x7001 | |

| Frequency[0] | 1 | uchar: 0 (122.88 MHz) | 0x8105 | 0x7005 | |

| Frequency[1] | 1 | uchar: 50 (50 MHz) | 0x8106 | 0x7006 | |

| Frequency[2] | 1 | uchar: 80 (80 MHz) | 0x8107 | 0x7007 | |

| Frequency[3] | 1 | uchar: 100 (100 MHz) | 0x8108 | 0x7008 | |

| Frequency[4] | 1 | uchar: 110 (110 MHz) | 0x8109 | 0x7009 | |

| Frequency[5] | 1 | uchar: 120 (120 MHz) | 0x810A | 0x700A | |

| Frequency[6] | 1 | uchar: 125 (125 MHz) | 0x810B | 0x700B | |

| unused | 3 | 0x810C | 0x700C | ||

| Channel 1 Gain F[0] | CG | 4 | float32 | 0x810F | 0x700F |

| Channel 1 Offset F[0] | CA | 4 | float32 | 0x8113 | 0x7013 |

| Channel 2 Gain F[0] | CG | 4 | float32 | 0x8117 | 0x7017 |

| Channel 2 Offset F[0] | CA | 4 | float32 | 0x811B | 0x701B |

| Channel 1 Gain F[1] | CG | 4 | float32 | 0x811F | 0x701F |

| Channel 1 Offset F[1] | CA | 4 | float32 | 0x8123 | 0x7023 |

| Channel 2 Gain F[1] | CG | 4 | float32 | 0x8127 | 0x7027 |

| Channel 2 Offset F[1] | CA | 4 | float32 | 0x812B | 0x702B |

| Channel 1 Gain F[2] | CG | 4 | float32 | 0x812F | 0x702F |

| Channel 1 Offset F[2] | CA | 4 | float32 | 0x8133 | 0x7033 |

| Channel 2 Gain F[2] | CG | 4 | float32 | 0x8137 | 0x7037 |

| Channel 2 Offset F[2] | CA | 4 | float32 | 0x813B | 0x703B |

| Channel 1 Gain F[3] | CG | 4 | float32 | 0x813F | 0x703F |

| Channel 1 Offset F[3] | CA | 4 | float32 | 0x8143 | 0x7043 |

| Channel 2 Gain F[3] | CG | 4 | float32 | 0x8147 | 0x7047 |

| Channel 2 Offset F[3] | CA | 4 | float32 | 0x814B | 0x704B |

| Channel 1 Gain F[4] | CG | 4 | float32 | 0x814F | 0x704F |

| Channel 1 Offset F[4] | CA | 4 | float32 | 0x8153 | 0x7053 |

| Channel 2 Gain F[4] | CG | 4 | float32 | 0x8157 | 0x7057 |

| Channel 2 Offset F[4] | CA | 4 | float32 | 0x815B | 0x705B |

| Channel 1 Gain F[5] | CG | 4 | float32 | 0x815F | 0x705F |

| Channel 1 Offset F[5] | CA | 4 | float32 | 0x8163 | 0x7063 |

| Channel 2 Gain F[5] | CG | 4 | float32 | 0x8167 | 0x7067 |

| Channel 2 Offset F[5] | CA | 4 | float32 | 0x816B | 0x706B |

| Channel 1 Gain F[6] | CG | 4 | float32 | 0x816F | 0x706F |

| Channel 1 Offset F[6] | CA | 4 | float32 | 0x8173 | 0x7073 |

| Channel 2 Gain F[6] | CG | 4 | float32 | 0x8177 | 0x7077 |

| Channel 2 Offset F[6] | CA | 4 | float32 | 0x817B | 0x707B |

| CRC | 1 | uchar | 0x817F | 0x707F |

Table 5. The EEPROM Memory Map

| Address | Function | Size (Bytes) |

|---|---|---|

| 0x7000 - 0x707F | User Calibration | 128 |

| 0x7080 - 0x70FF | Future Use | 128 |

At the power up the EEPROM memory is protected against write operations. To disable the write protection one has to write a magic number to a magic address over I2C. To re-enable the write protection one has to write any other number to the magic address.

Table 6. The Write Protection Disable magic number and address

| Magic Number | Magic Address |

|---|---|

| 0xD2 | 0x6FFF |

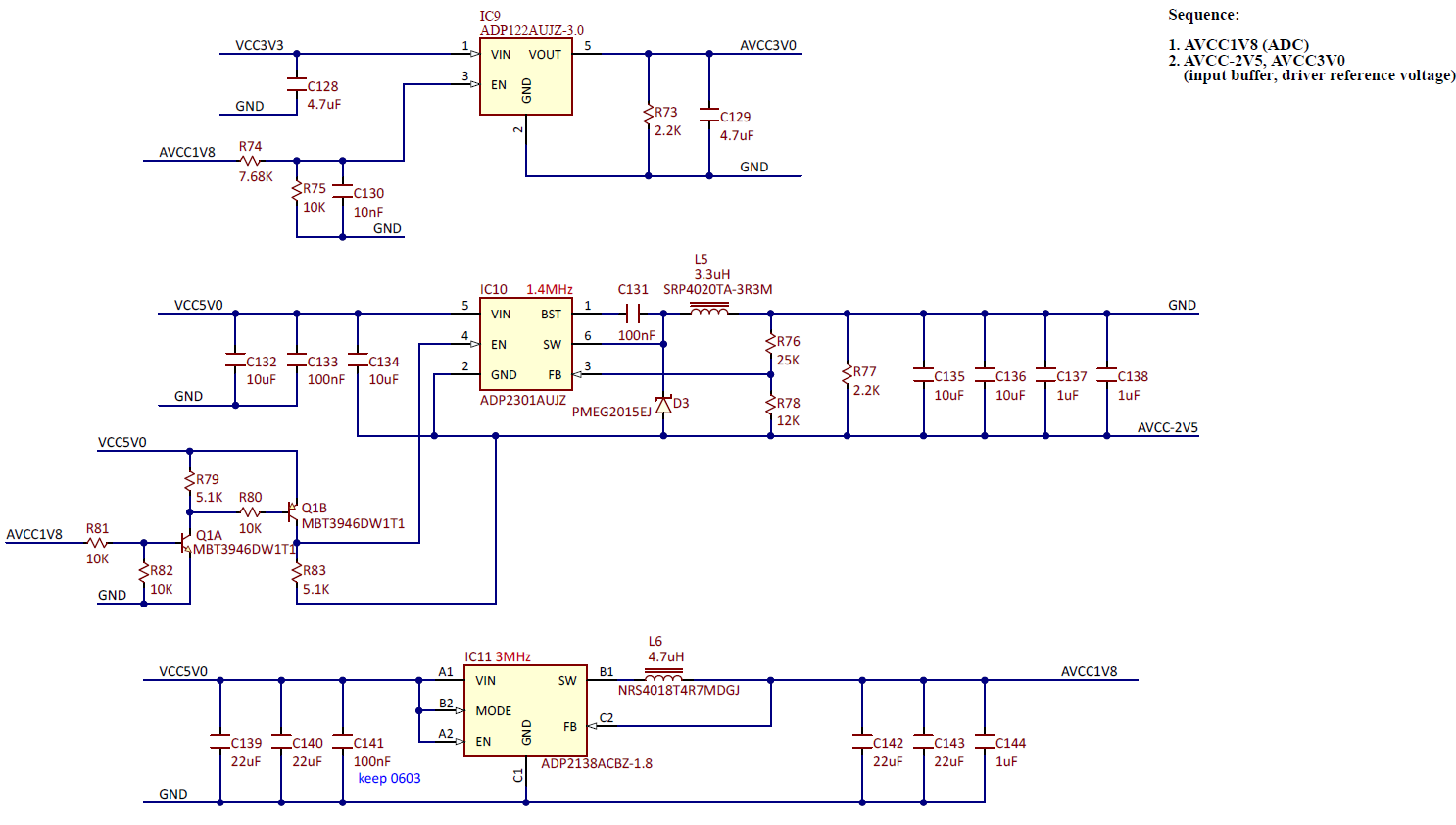

4. Power Supplies and Control

This block includes the internal power supplies.

The Zmod Digitizer gets the digital rails from the carrier board, via the SYZYGY connector:

- VCC5V0 - used for analog supplies

- VCC3V3 - used for the MCU and analog supplies

- Vadj = 1.8 V - used for the ADC digital rail

The internal analog rails sequence is:

- AVCC1V8 - ADC analog rail

- AVCC3V0 - Buffer, reference voltage, ADC driver

- AVCC-2V5 - Buffer, reference voltage

4.1. AVCC1V8

The analog supply AVCC1V8 is built from VCC5V0 using IC11, an ADP2138 Fixed Output Voltage, 800mA, 3MHz, Step-Down DC-to-DC converter. To insure low output voltage ripple a second LC filter (FB11 in Fig. 4) is added and forced PWM mode is selected.

- Input voltage: 2.3 V to 5.5 V

- Peak efficiency: 95%

- 3 MHz fixed frequency operation

- Typical quiescent current: 24 μA

- Very small solution size

- 6-lead, 1 mm × 1.5 mm WLCSP package

- Fast load and line transient response

- 100% duty cycle low dropout mode

- Internal synchronous rectifier, compensation, and soft start

- Current overload and thermal shutdown protections

- Ultra-low shutdown current: 0.2 μA (typical)

- Forced PWM and automatic PWM/PSM modes

4.2. AVCC3V0

The analog supply AVCC3V0 is built from VCC3V3 using IC9, an ADP122 5.5 V Input, 300 mA, Low Quiescent Current, CMOS Linear Regulator, Fixed Output Voltage. To reduce noise and reduce the crosstalk between supplied circuits, the rail uses individual LC filters: FB13 in Fig. 3, and others (not shown).

- Input voltage supply range: 2.3 V to 5.5 V

- 300 mA maximum output current

- Fixed and adjustable output voltage versions

- Very low dropout voltage: 85 mV at 300 mA load

- Low quiescent current: 45 µA at no load

- Low shutdown current: <1 µA

- Initial accuracy: ±1% accuracy

- Up to 31 fixed-output voltage options available from

- 1.75 V to 3.3 V

- Adjustable-output voltage range

- 0.8 V to 5.0 V (ADP123)

- Excellent PSRR performance: 60 dB at 100 kHz

- Excellent load/line transient response

- Optimized for small 1.0 μF ceramic capacitors

- Current limit and thermal overload protection

- Logic-controlled enable

- Compact packages: 5-lead TSOT and 6-lead 2 mm × 2 mm LFCSP

4.4. AVCC-2V5

The AVCC-2V5 analog power supply is implemented with the ADP2301 Step-Down regulator in an inverting Buck-Boost configuration. See application Note AN-1083: Designing an Inverting Buck Boost Using the ADP2300 and ADP2301. To reduce noise and reduce the crosstalk between supplied circuits, the rail uses individual LC filters. The ADP2301 features:

- 1.2 A maximum load current

- ±2% output accuracy over temperature range

- 1.4 MHz switching frequency

- High efficiency up to 91%

- Current-mode control architecture

- Output voltage from 0.8 V to 0.85 × VIN

- Automatic PFM/PWM mode switching

- Integrated high-side MOSFET and bootstrap diode,

- Internal compensation and soft start

- Undervoltage lockout (UVLO), Overcurrent protection (OCP) and thermal shutdown (TSD)

- Available in ultrasmall, 6-lead TSOT package

5. The SYZYGY™ Connector

The SYZYGY™ connector in provides the interface with the carrier board. The used signals are:

- Power rails

- VCC5V0

- VCC3V3

- VADJ - needs to be set by the carrier board to 1.8V

- GND

- Shield

- SYZYGY™ I2C bus:

- MCU_SCL_USCK

- MCU_SDA_MOSI

- FPGA generated differential clock (alternate for local CDCE clock)

- CLK_PLL_P

- CLK_PLL_N

- ADC single-ended output clock:

- CLKOUT_ADC (coupled with GND in the differential P2C pair)

- R_GA for geographical address identification

- SYNC_ADC for ADC internal clock divider synchronization

- ADC data bus: DOUT_ADC_0…13

- ADC SPI bus:

- CS_SC1n

- SCLK_SC

- SDIO_SC

- CDCE control signals

- CDCE_REFSEL

- CDCE_HW_SW_CTRL

- CDCE_PDN

- CDCE_GPIO_1

- CDCE_GPIO_4

- CDCE I2C bus

- CDCE_SCL

- CDCE_SDA

6. The SYZYGY™ compatibility table

Table 7. The SYZYGY™ compatibility table

| Parameter | Value |

|---|---|

| Maximum 5V supply current | 400 mA |

| Maximum 3.3V supply current | 100 mA |

| VIO supply voltage | 1.8 V |

| Maximum VIO supply current | 270 mA |

| Total number of I/O | 28 |

| Number of differential I/O pairs | 0 |

| Width | Single |

Written by Mircea Dabacan, PhD, Technical University of Cluj-Napoca Romania