Virtex-5 OpenSPARC Reference Manual

Note

The Virtex-5 OpenSPARC is retired and no longer for sale in our store.

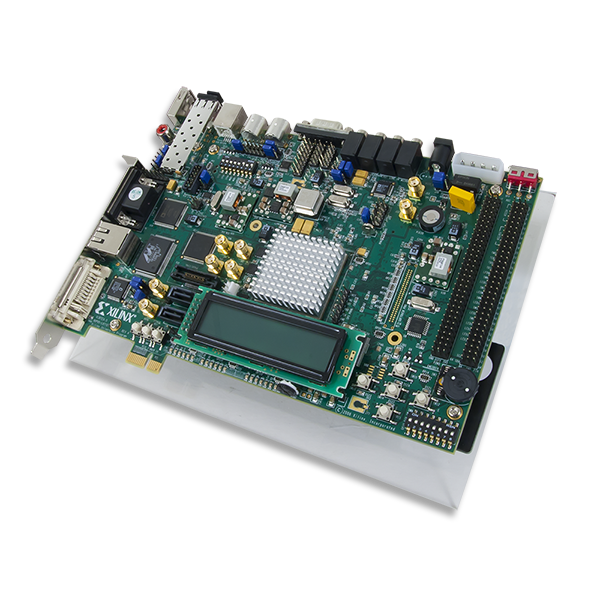

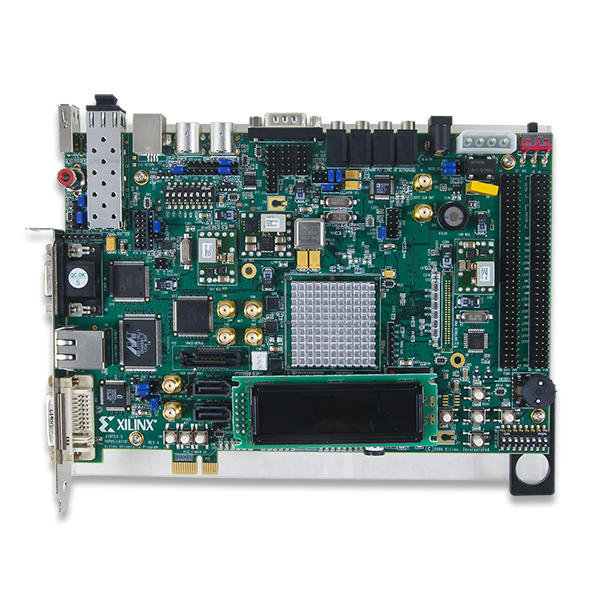

The Virtex®-5 OpenSPARC Evaluation Platform is a powerful system for hosting the OpenSPARC T1 open-source microprocessor. Equivalent to the Xilinx® ML509 board and based on the Xilinx XUPV5-LX110T FPGA, this kit brings the throughput of OpenSPARC Chip Multi-Threading to an FPGA.

OpenSPARC T1 is the open-sourced version of the custom designed UltraSPARC T1 microprocesor from Sun Microsystems. To broaden the appeal of this state-of-the-art Chip Multi-threading (CMT) technology to the developers, engineers at Sun Microsystems and Xilinx Inc. have developed a reference design that allows a scaled-down version of the OpenSPARC T1 processor to run on Xilinx Virtex-5 FPGAs. This reference design is an excellent starting point for researchers and entrepreneurs to build and test novel ideas in the areas of computer architecture, logic design, parallel programming, and compiler techniques, among others. For more details on how to download the OpenSPARC design and the reference design, please visit www.opensparc.net/fpga.

Features

- Xilinx Virtex-5 FPGA

- XC5VLX50T-1FFG1136 (ML505)

- XC5VSX50T-1FFG1136 (ML506)

- XC5VFX70T-1FFG1136 (ML507)

- Two Xilinx XCF32P Platform Flash PROMs (32 Mb each) for storing large device configurations

- Xilinx System ACE™ CompactFlash configuration controller with Type I CompactFlash connector

- Xilinx XC95144XL CPLD for glue logic

- 64-bit wide, 256-MB DDR2 small outline DIMM (SODIMM), compatible with EDK supported IP and software drivers

- Clocking

- Programmable system clock generator chip

- One open 3.3V clock oscillator socket

- External clocking via SMAs (two differential pairs)

- General purpose DIP switches (8), LEDs (8), pushbuttons, and rotary encoder

- Expansion header with 32 single-ended I/O, 16 LVDS-capable differential pairs,

- 14 spare I/Os shared with buttons and LEDs, power, JTAG chain expansion capability, and IIC bus expansion

- Stereo AC97 audio codec with line-in, line-out, 50-mW headphone, microphone-in jacks, SPDIF digital audio jacks, and piezo audio transducer

- 12 www.xilinx.com ML505/ML506/ML507 Evaluation Platform UG347 (v3.1.2) May 16, 2011 Chapter 1: ML505/ML506/ML507 Evaluation Platform R

- RS-232 serial port, DB9 and header for second serial port

- 16-character x 2-line LCD display

- One 8-Kb IIC EEPROM and other IIC capable devices

- PS/2 mouse and keyboard connectors

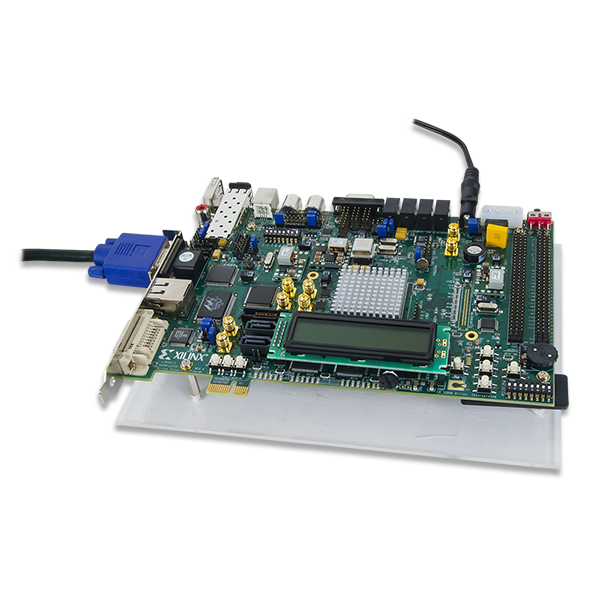

- Video input/output

- Video input (VGA)

- Video output DVI connector (VGA supported with included adapter)

- ZBT synchronous SRAM, 9 Mb on 32-bit data bus with four parity bits

- Intel P30 StrataFlash linear flash chip (32 MB)

- Serial Peripheral Interface (SPI) flash (2 MB)

- 10/100/1000 tri-speed Ethernet PHY transceiver and RJ-45 with support for MII, GMII, RGMII, and SGMII Ethernet PHY interfaces

- USB interface chip with host and peripheral ports

- Rechargeable lithium battery to hold FPGA encryption keys

- JTAG configuration port for use with Parallel Cable III, Parallel Cable IV, or Platform USB download cable

- Onboard power supplies for all necessary voltages

- Temperature and voltage monitoring chip with fan controller

- 5V @ 6A AC adapter

- Power indicator LED

- MII, GMII, RGMII, and SGMII Ethernet PHY Interfaces

- GTP/GTX: SFP (1000Base-X)

- GTP/GTX: SMA (RX and TX Differential Pairs)

- GTP/GTX: SGMII

- GTP/GTX: PCI Express® (PCIe™) edge connector (x1 Endpoint)

- GTP/GTX: SATA (dual host connections) with loopback cable

- GTP/GTX: Clock synthesis ICs

- Mictor trace port

- BDM debug port

- Soft touch port

- System monitor